### THE UNIVERSITY OF MICHIGAN

Memorandum 13

## SYSTEM/360 INTERFACE ENGINEERING REPORT

David Mills

CONCOMP: Research in Conversational Use of Computers

ORA Project 07449

F.H. Westervelt, Director

supported by:

DEPARTMENT OF DEFENSE ADVANCED RESEARCH PROJECTS AGENCY WASHINGTON, D.C.

CONTRACT NO. DA-49-083 OSA-3050 ARPA ORDER NO. 716

administered through:

OFFICE OF RESEARCH ADMINISTRATION ANN ARBOR

November 1967

#### PREFACE

The System/360 interface provides a connection between the PDP-8 and the multiplexor channel of System/360 models 30, 40, and 50, as well as the 2870 Multiplexor Channel attached to other models. Either byte-interleaved or burst-mode operation can be sustained at transmission rates up to 70 kilobytes-per-second. Interface control operations are supervised via the PDP-8 accumulator and interrupt facilities, while data transfer operations are directed via the three-cycle data break facility. The interface is attached directly to the channel-control unit interface cables which interconnect the IBM equipment and occupies one control unit position on the channel. The equipment satisfies all original equipment manufacturer's (OEM) specifications as described in the following IBM publications:

- 1. System/360 I/O Interface: Channel to Control Unit Original Equipment Manufacturer's Information, IBM Corporation, Form A22-6843-3.

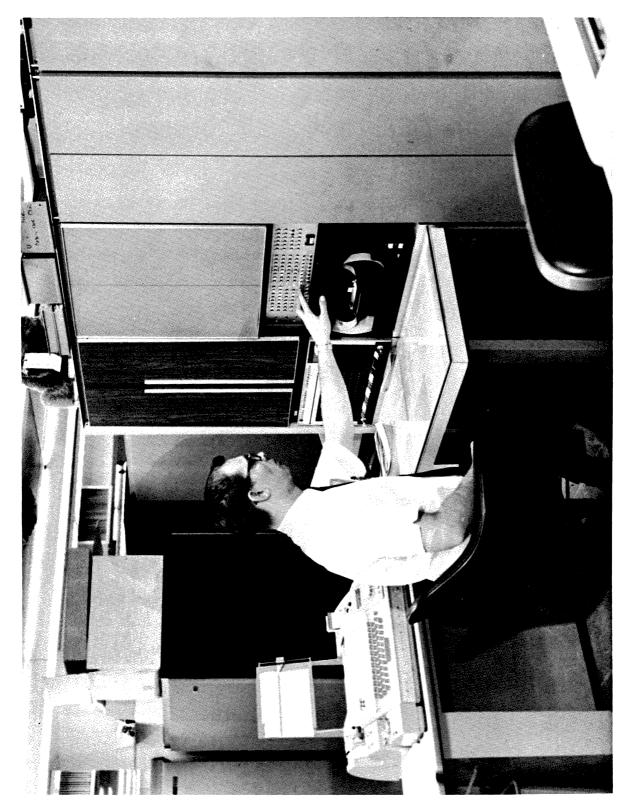

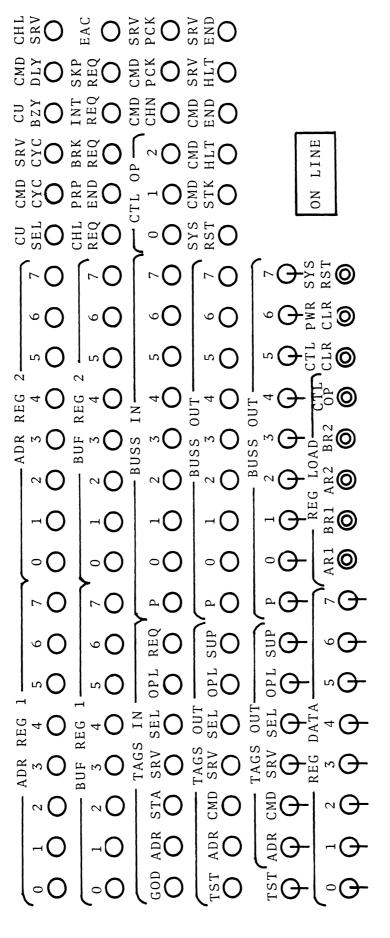

The accompanying photographs on the next two pages show the Data Concentrator, including the System/360 interface together with its test panel. The interface itself is assembled in the bays immediately above the test panel.

The Data Concentrator. The Interface is in the Bay immediately above the Test Panel. Figure i.

Figure ii. The Test Panel of the Interface.

### ACKNOWLEDGMENTS

In the design of the equipment described herein, Mr. Dan Pence transcribed the logical functions to DEC Flip-Chip technology and constructed the working documentation, consisting of logic diagrams and computer-generated punched-card wiring lists. Working from these wiring lists, the Gardner-Denver Company of Grand Haven, Michigan, constructed the Flip-Chip mounting panels using automatic wire-wrap machinery. Mr. Ken Burkhalter designed the IBM-DEC interface circuit boards and power control equipment described in Appendix D. Panel, described in Appendix F, was constructed using photographic techniques by the Prin-Tek Company of Detroit, Michigan. All the special printed-circuit components were supplied by the Photo Tek Company of Ann Arbor. Mr. David Flower and Mr. Warren Kennison assembled the equipment in a most craftsmanlike fashion.

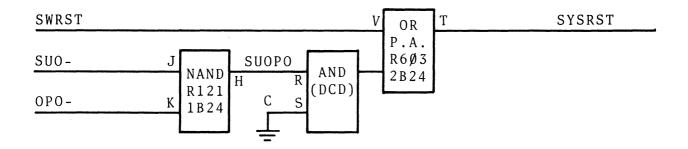

The IBM company provided documentation which was invaluable in the design of this equipment. In particular, Mr. Les Bailey and Mr. Dan Murphy, both of IBM, have contributed much useful advice.

## TABLE OF CONTENTS

|       |                                 |                          |                                       |                      |                 |       |         |         |       |           |       |                                       |       |     |   | Page                       |

|-------|---------------------------------|--------------------------|---------------------------------------|----------------------|-----------------|-------|---------|---------|-------|-----------|-------|---------------------------------------|-------|-----|---|----------------------------|

| PREF  | ACE.                            |                          |                                       |                      |                 |       |         | • • • • | • . • |           | • •   | • • •                                 |       |     |   | iii                        |

| ACKNO | OWLE                            | DGMEN                    | TS                                    | • • • •              |                 | • • • |         |         | •     |           |       |                                       |       |     |   | vii                        |

| LIST  | OF I                            | FIGUR                    | ES                                    |                      |                 |       |         |         |       |           |       |                                       |       |     |   | xiii                       |

| I     | INT                             | RODUC                    | TION.                                 | • • • •              |                 | c • o | • • •   |         |       |           |       |                                       |       |     | • | 1                          |

| ΙΙ    | CHAI                            | NNEL                     | INTER                                 | RFACE                | LI              | NES   |         |         |       |           |       |                                       |       |     |   | 2                          |

|       |                                 | BUS<br>Out<br>Inb<br>Sel | OUT. IN bound ound ectic              | Tags                 | s               | ols   | · · ·   | • • • • | • • • | • • • •   | • • • | · · · · · · · · · · · · · · · · · · · | • • • | • • |   | 2<br>2<br>4<br>4<br>4<br>5 |

| III   | CONT                            | rol :                    | SEQUE                                 | NCES                 |                 |       | • • •   |         |       | . <b></b> |       |                                       |       |     |   | 5                          |

|       | 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Ser<br>Spe<br>Pol        | tial<br>vice<br>cial<br>ling<br>ipmen | Cycl<br>Sequ<br>Oper | e<br>enc<br>ati | es.   | • • • • |         | • • • | • • •     | • • • |                                       |       |     |   | 6<br>9<br>12<br>14<br>18   |

| ΙV    |                                 | GRAMM<br>ERFACI          |                                       |                      |                 |       |         |         |       |           |       |                                       |       |     |   | 19                         |

|       | 4.1<br>4.2<br>4.3               | Ser                      | mand<br>vice<br>tem/3                 | Inte                 | rfa             | ce (  | ) per   | ati     | ions  | s         |       |                                       |       |     |   | 2 2<br>2 6<br>3 6          |

|       |                                 | Hal <sup>r</sup><br>Tes  | rt I/<br>t I/O<br>t I/O<br>gramm      | )<br>!               |                 | · · · | • • • • |         |       |           | • • • | • • •                                 | • • • | • • |   | 37<br>37<br>38<br>39       |

| V     | ARCI                            | HITEC                    | ΓURE                                  | OF S                 | YST             | EM/   | 360     | INT     | ΓΕΝΙ  | FAC       | Ε     |                                       |       |     |   | 39                         |

| APPEN | NDIX                            | Α                        |                                       | • • • •              |                 | • • • | • • •   |         |       |           | • • • |                                       |       |     |   | 62                         |

| APPEN | NDIX                            | B                        |                                       |                      |                 |       | • • •   |         |       | • • •     | • • • |                                       |       |     |   | 73                         |

| APPEN | NDIX                            | C                        | • • • • •                             | • • • •              | • • •           | • • • | • • •   |         |       |           |       |                                       |       |     |   | 83                         |

|       | ANAI                            | LYSIS                    | OF S                                  | ELEC                 | T L             | ATCI  | 1 C]    | RCU     | JITI  | RY.       |       |                                       |       |     |   | . 85                       |

| APPEN | NDIX                            | D                        |                                       |                      | e • •           | • • • |         |         |       |           |       |                                       | • • • |     |   | . 88                       |

|       | ADD                             | TION                     | AL CO                                 | NSTR                 | UCT             | ION   | DET     | CAII    | LS.   |           |       |                                       |       |     |   | . 90                       |

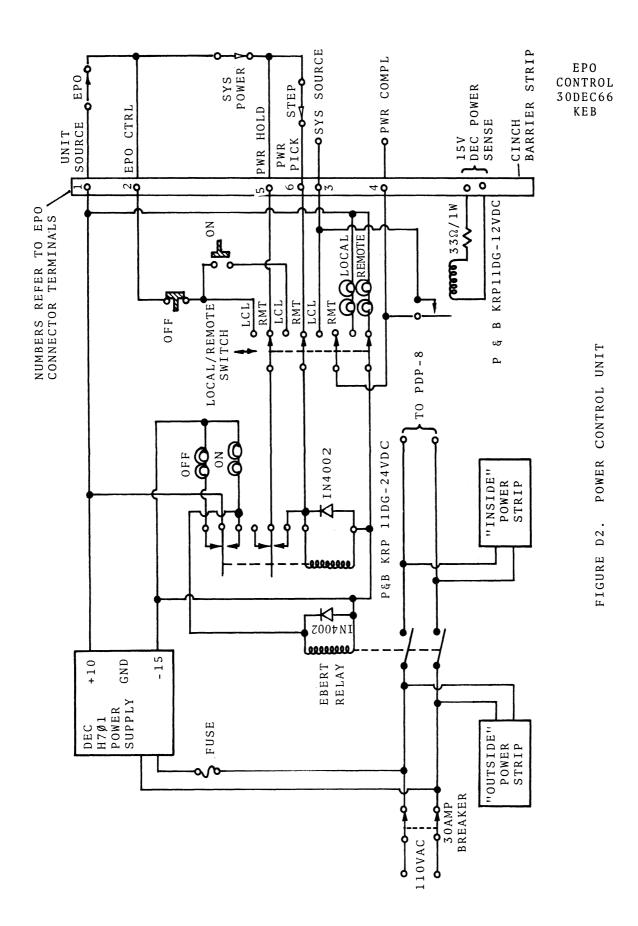

|       |                                 | D 1<br>D 2<br>D 3        | Powe                                  | em C<br>r Co<br>DEC  | ntr             | ol l  | Jnit    |         |       |           |       |                                       |       |     |   | . 92                       |

# TABLE OF CONTENTS (cont'd)

|          |                | Page |

|----------|----------------|------|

| APPENDIX | E              | 99   |

| APPENDIX | F              | 145  |

|          | The Test Panel |      |

# LIST OF FIGURES

| <u>Figure</u> |                                                         | Page |

|---------------|---------------------------------------------------------|------|

| i             | The Data Concentrator                                   | iv   |

| ii            | The Test Panel of the Interface                         | ν    |

| 1             | Channel-Control Unit Interface Lines                    | 3    |

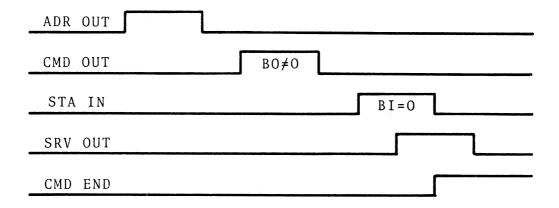

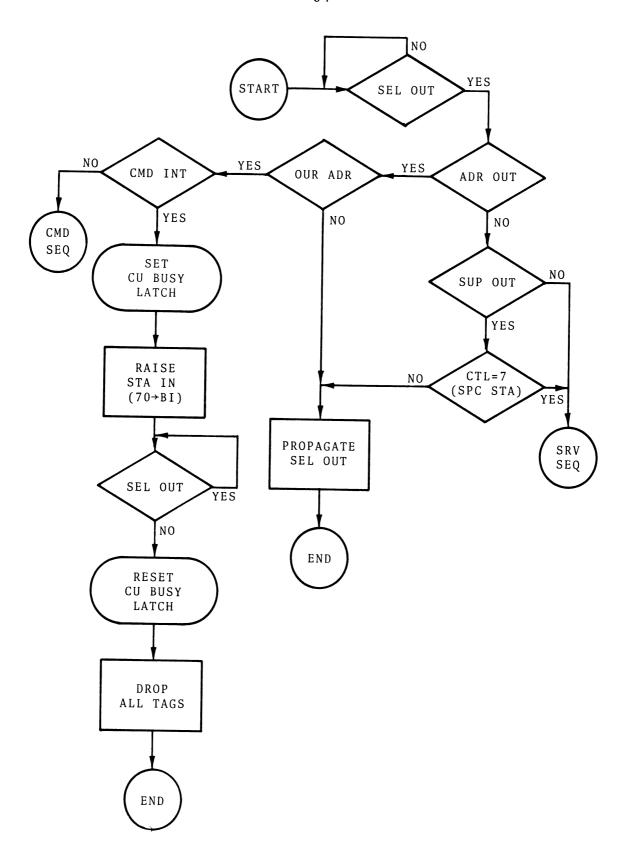

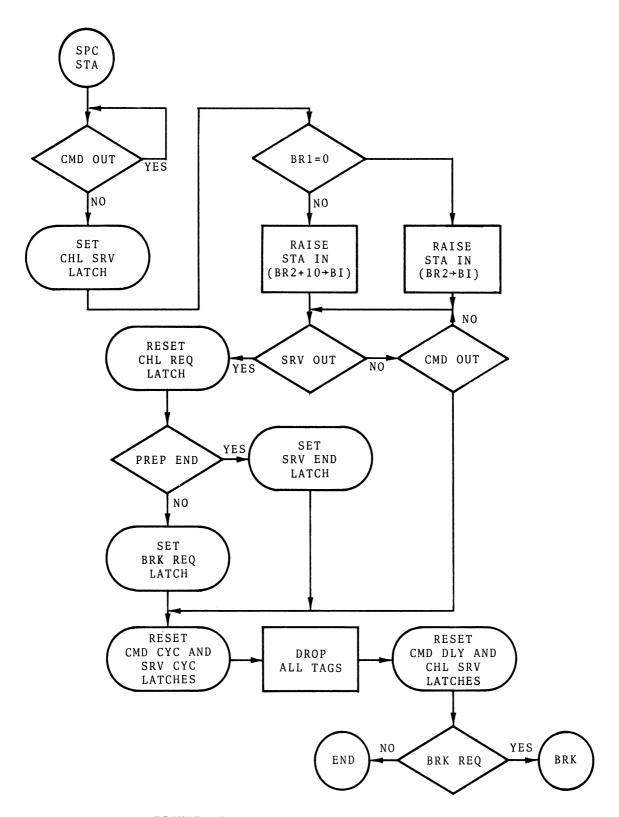

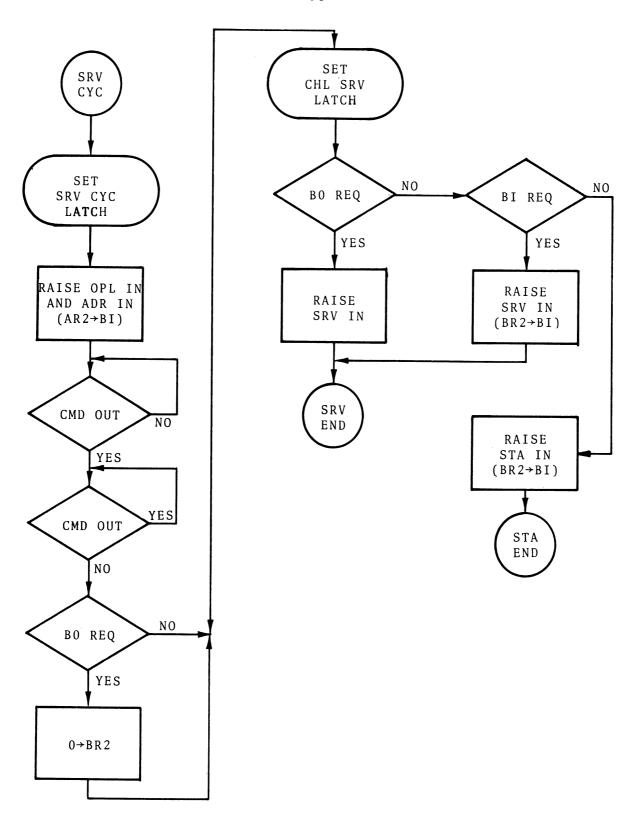

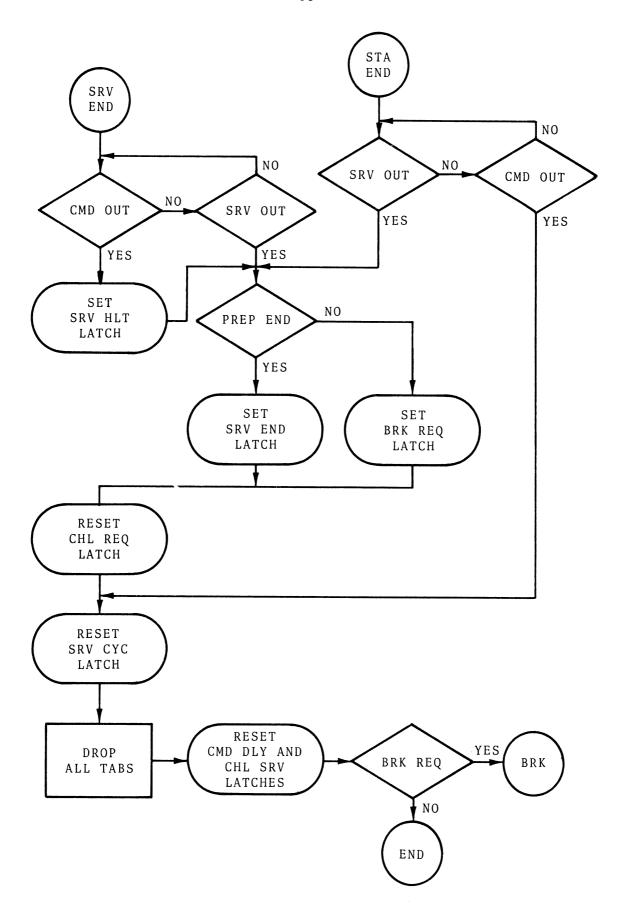

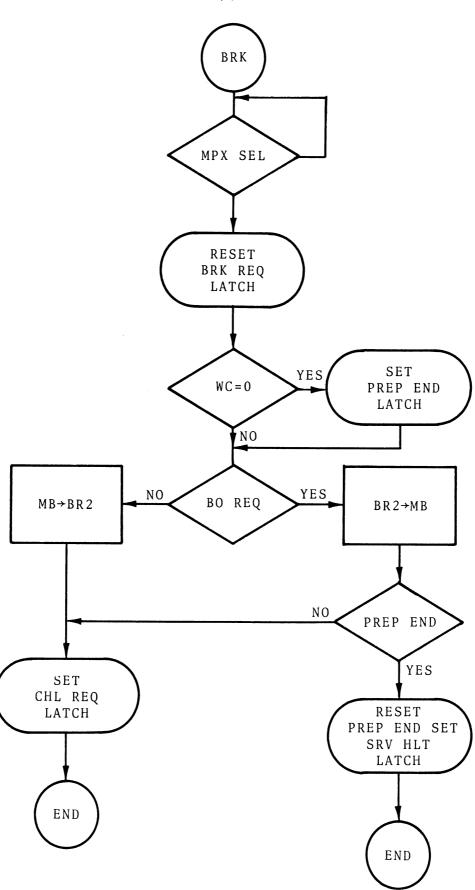

| 2             | Initial Selection                                       | 7    |

| 3             | Service Cycle (Burst Mode)                              | 10   |

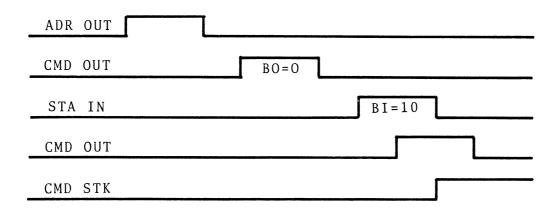

| 4             | Interface Disconnect                                    | 13   |

| 5             | Control Unit Busy                                       | 16   |

| 6             | Register Bit Assignments                                | 21   |

| 7             | Initial Selection-HIO                                   | 23   |

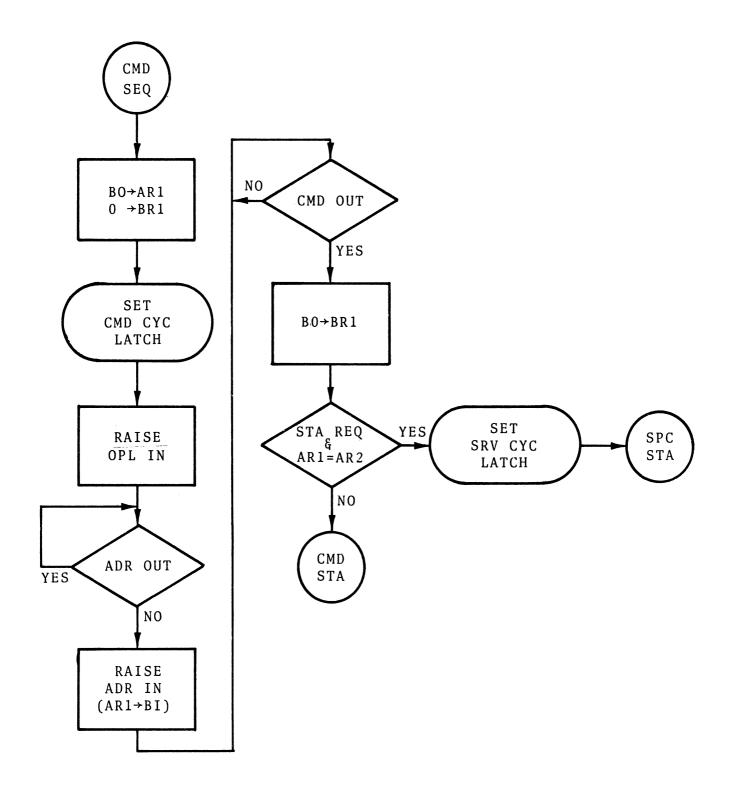

| 8 a           | Service Cycle—Stop                                      | 27   |

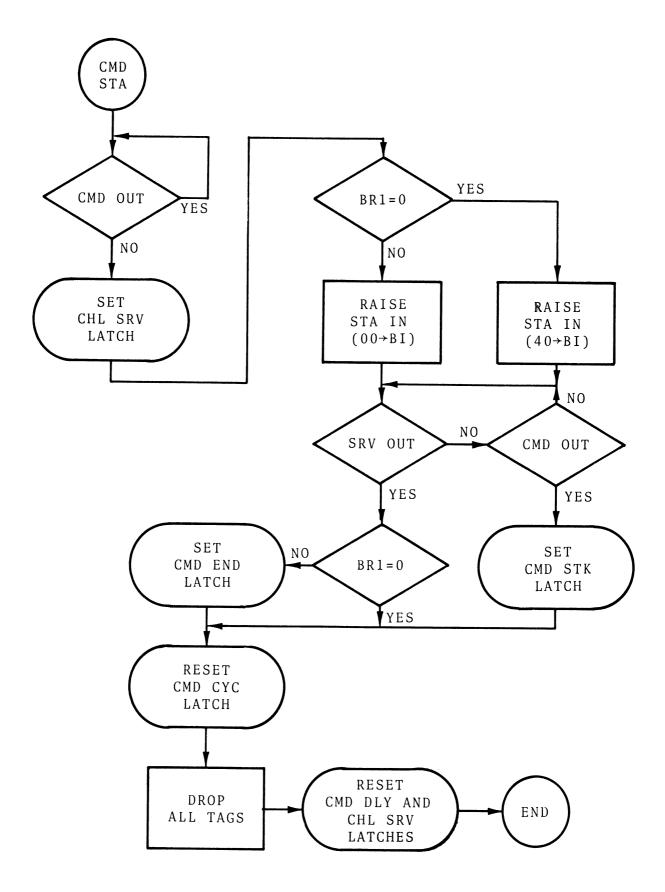

| 8 b           | Service Cycle-End                                       | 28   |

| 9             | Principal Interface Components                          | 40   |

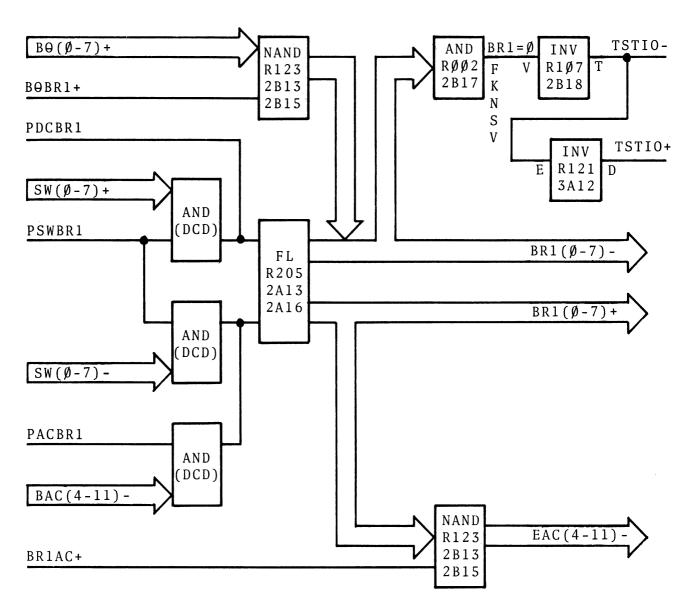

| 10a           | AR1, BR1, AR2 Registers                                 | 43   |

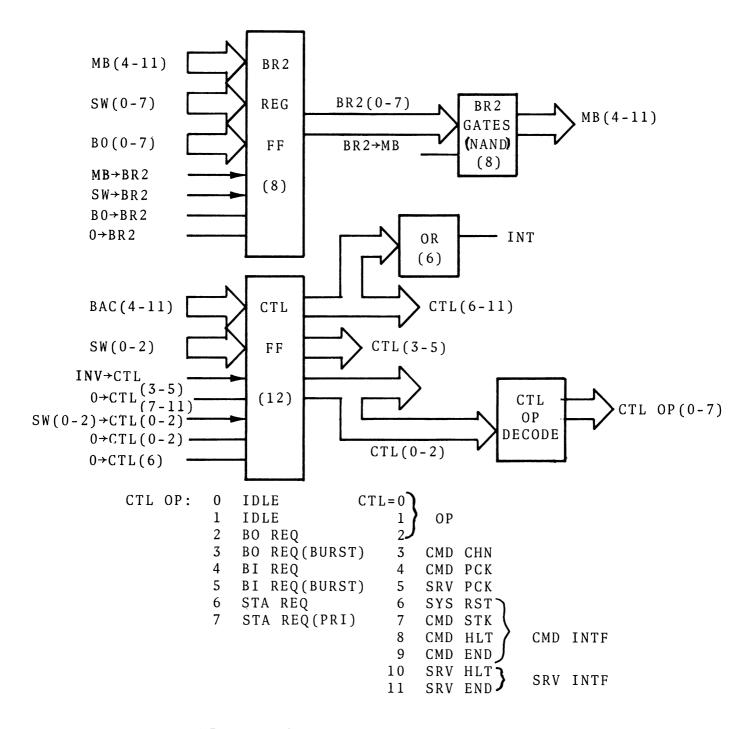

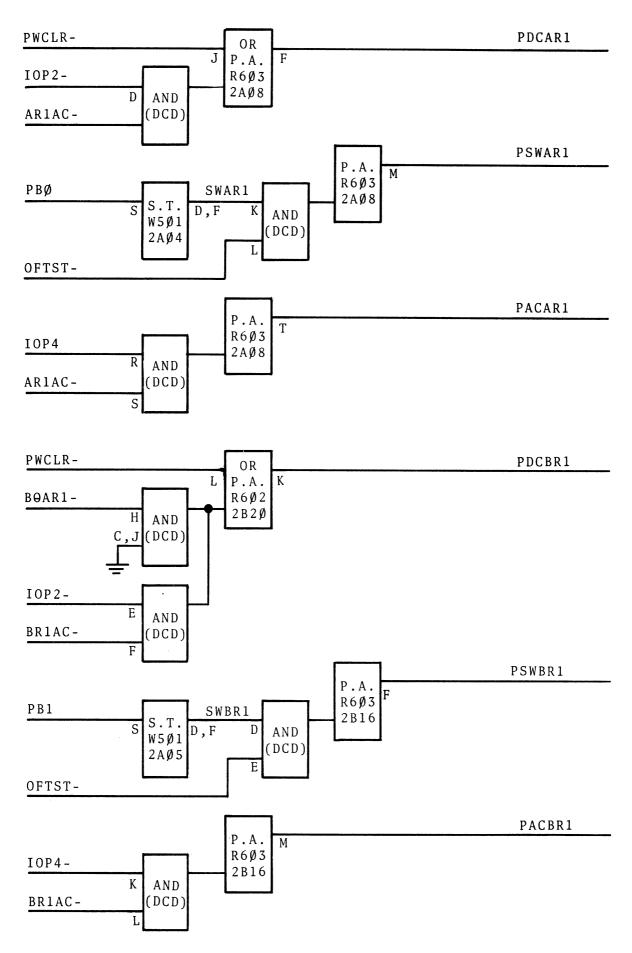

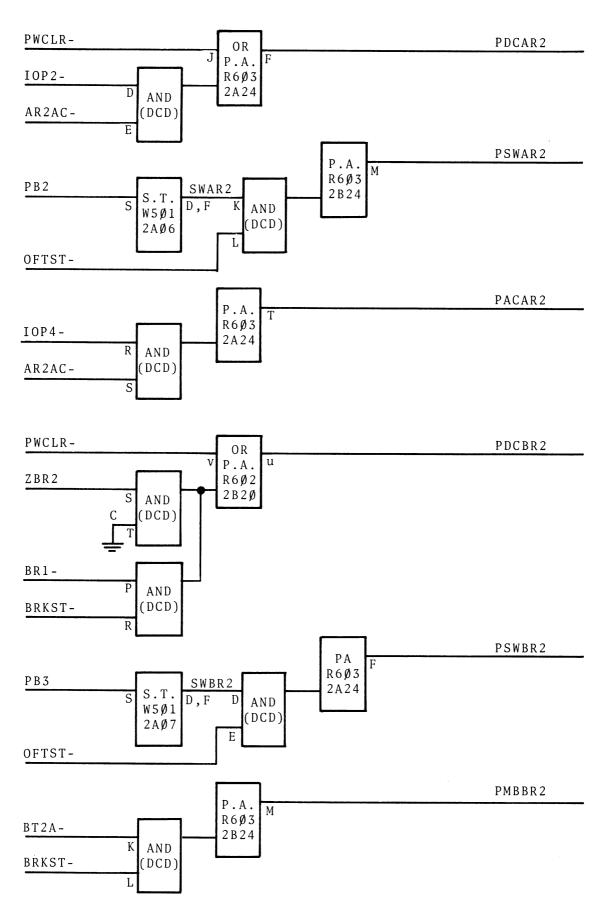

| 10b           | BR2 and CTL Registers                                   | 44   |

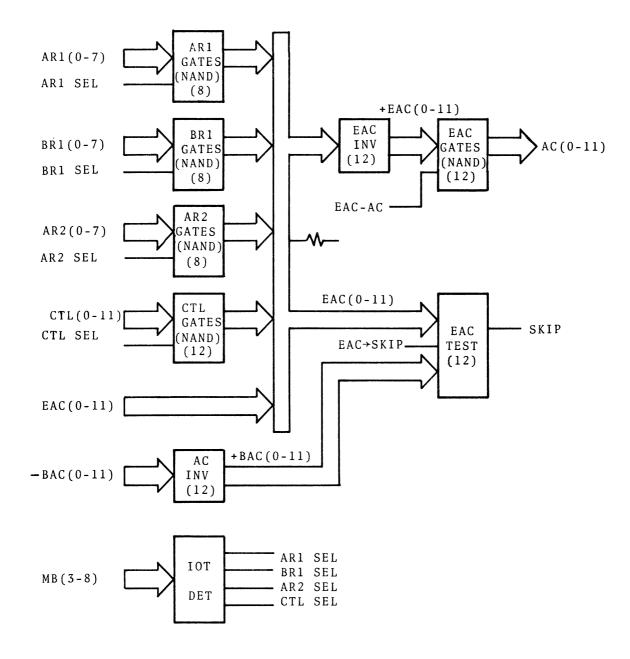

| 11            | PDP-8 Data Paths                                        | 45   |

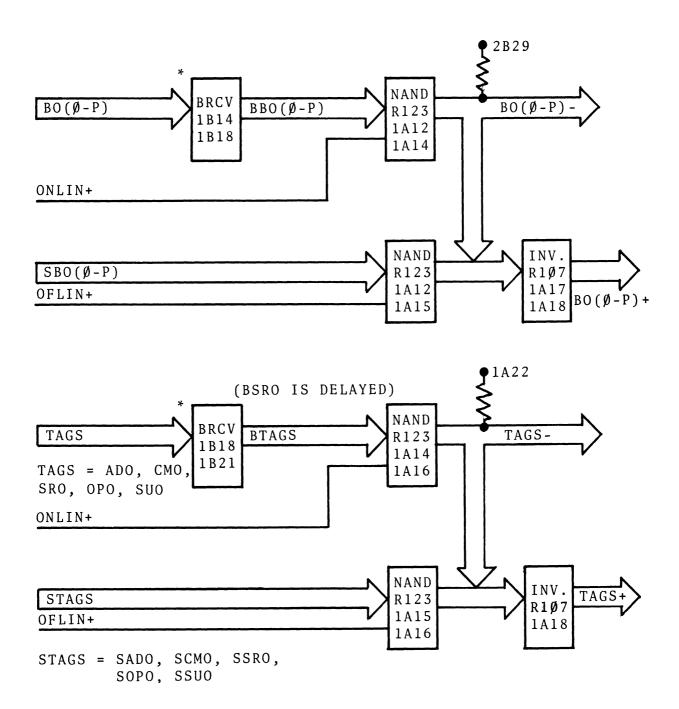

| 12            | Bus Gating                                              | 46   |

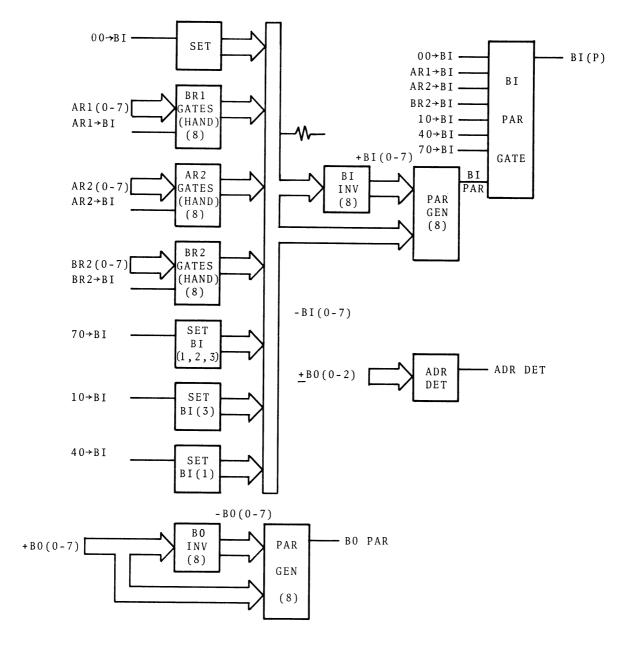

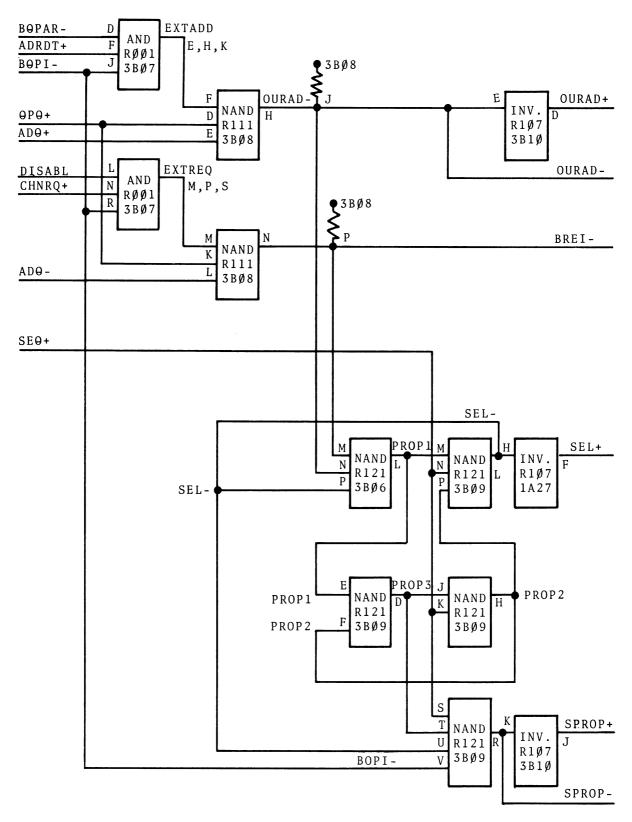

| 13            | Select Interception                                     | 48   |

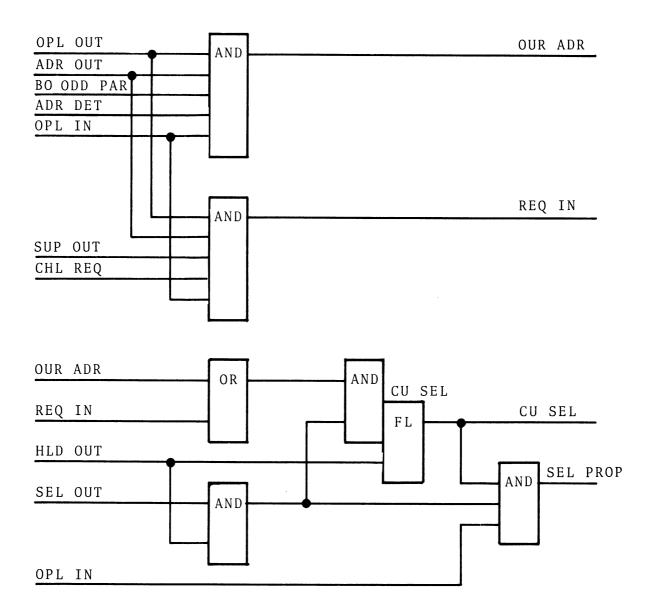

| 14            | Channel Seizure                                         | 49   |

| 15            | Command Storage/Proceed                                 | 51   |

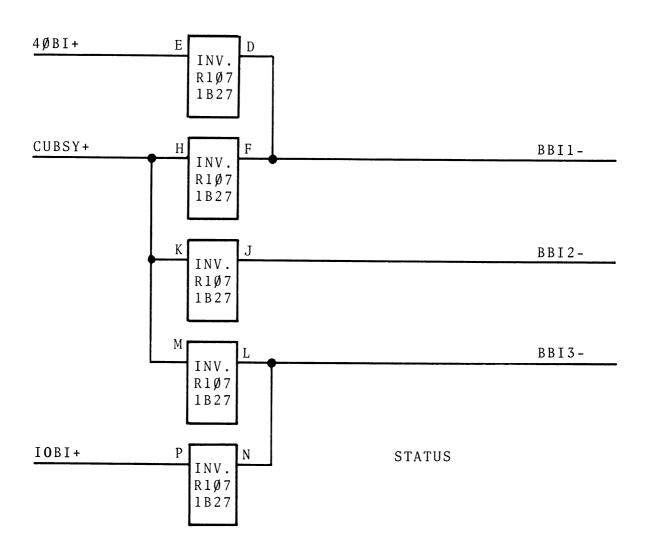

| 16            | Status                                                  | 52   |

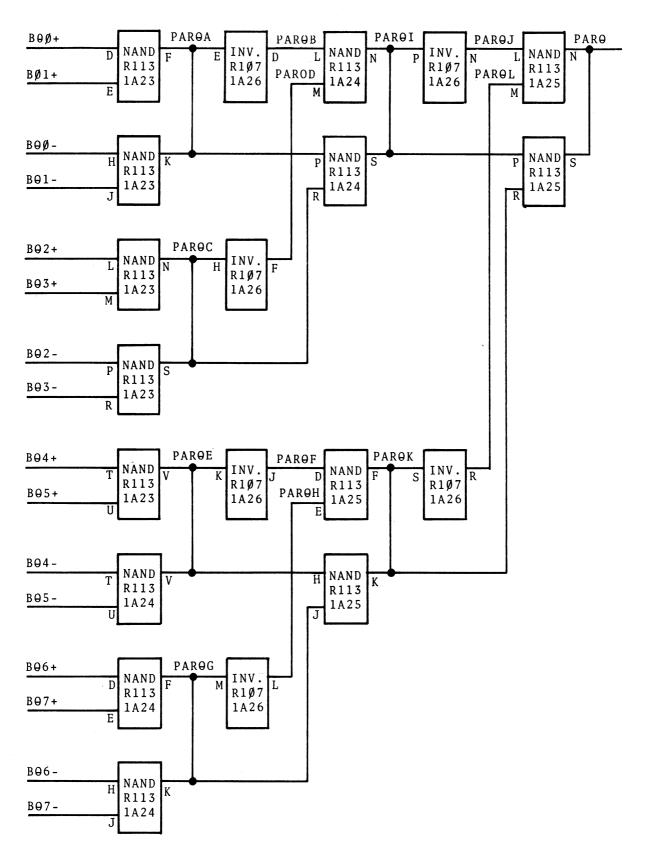

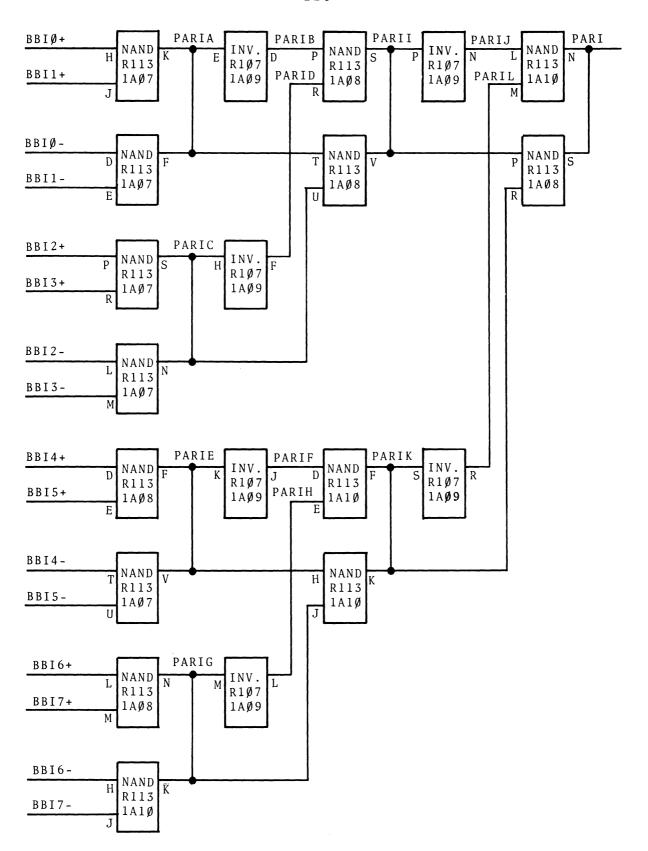

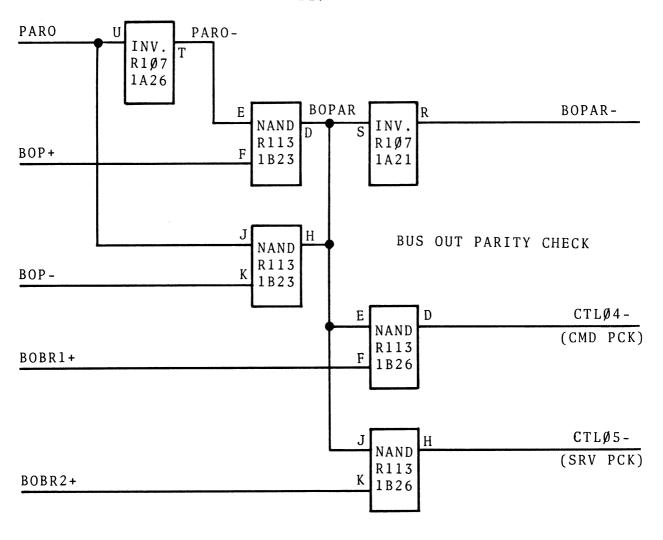

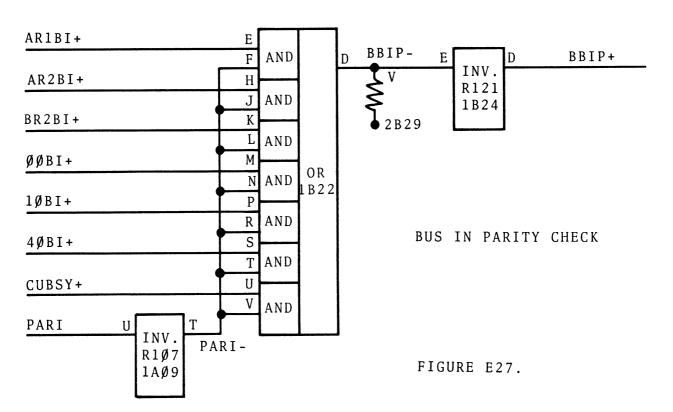

| 17            | Parity Check                                            | 53   |

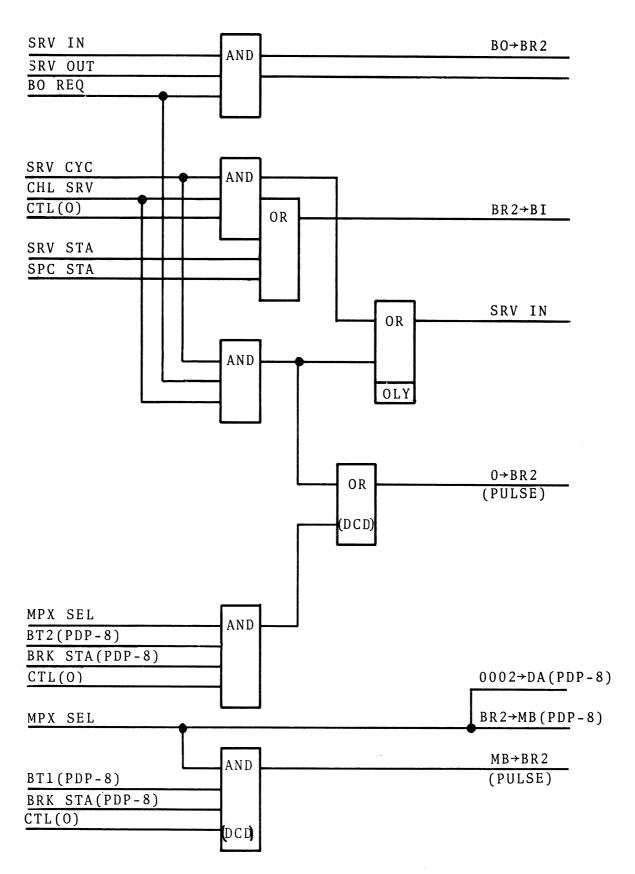

| 18            | BR2 Gating                                              | 55   |

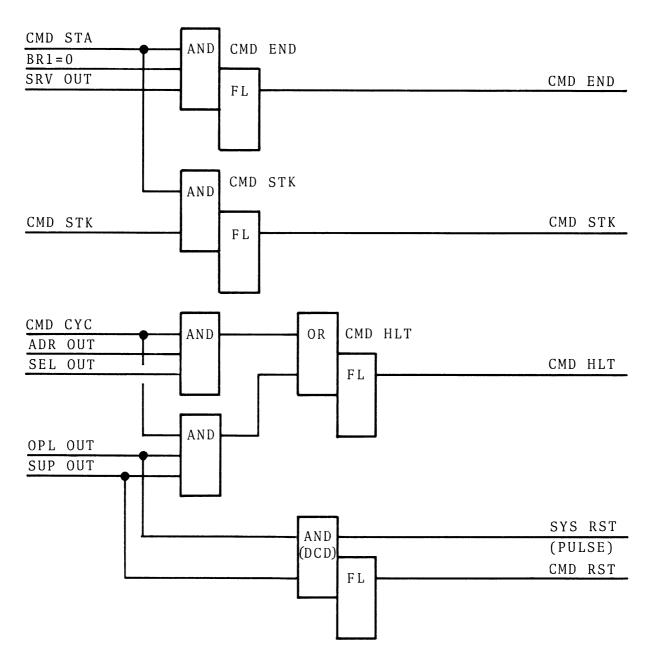

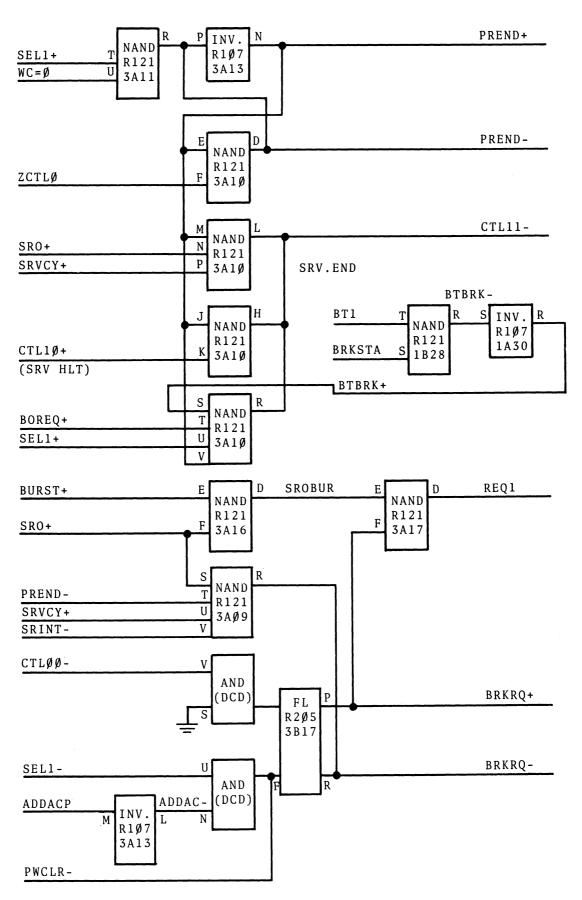

| 19            | Command End                                             | 56   |

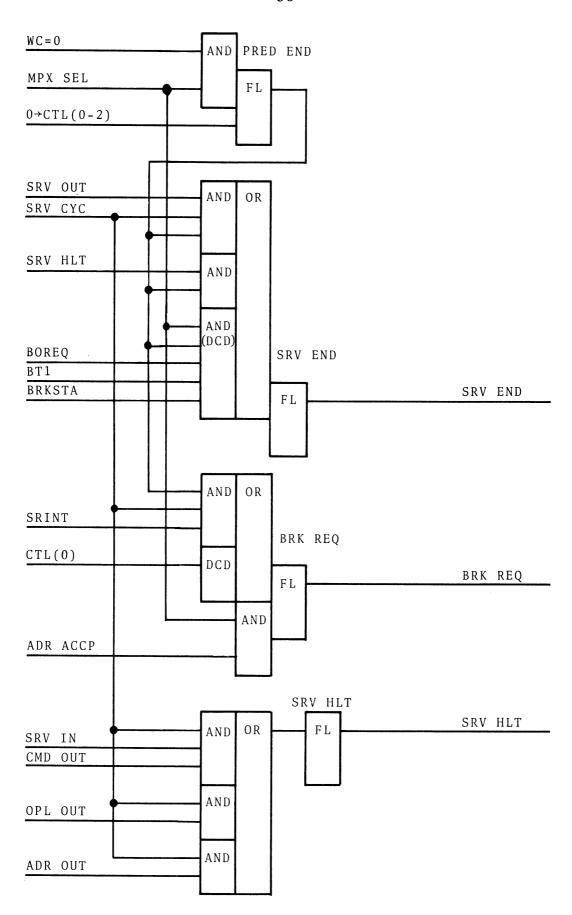

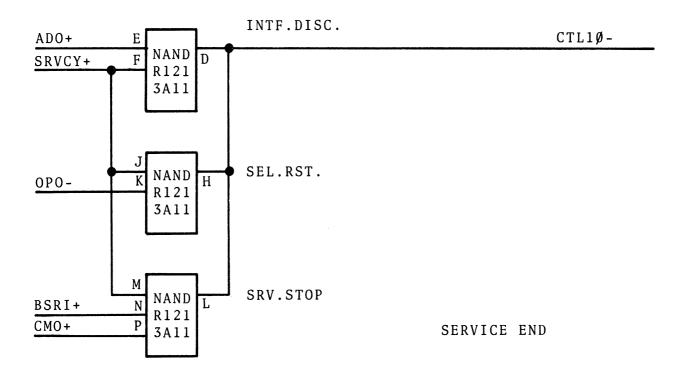

| 20            | Service End                                             | 58   |

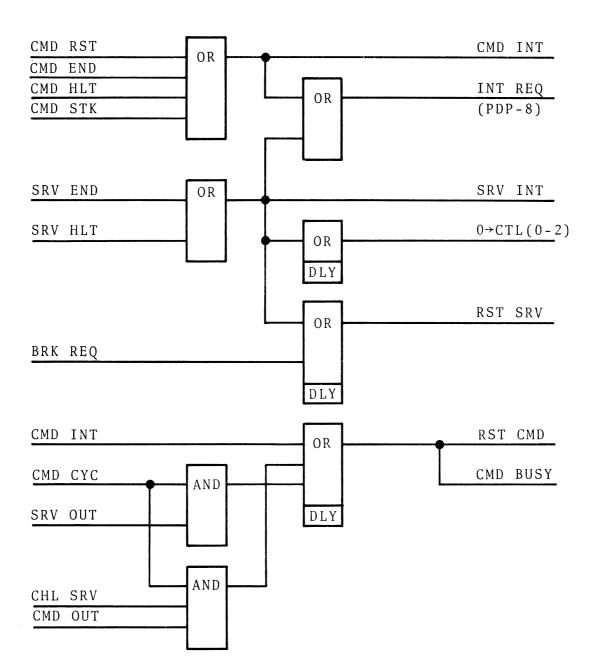

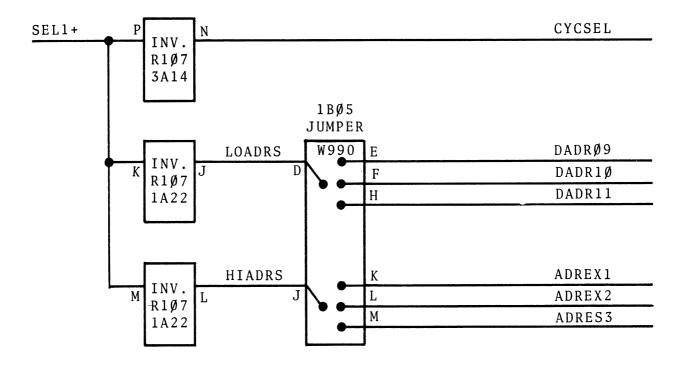

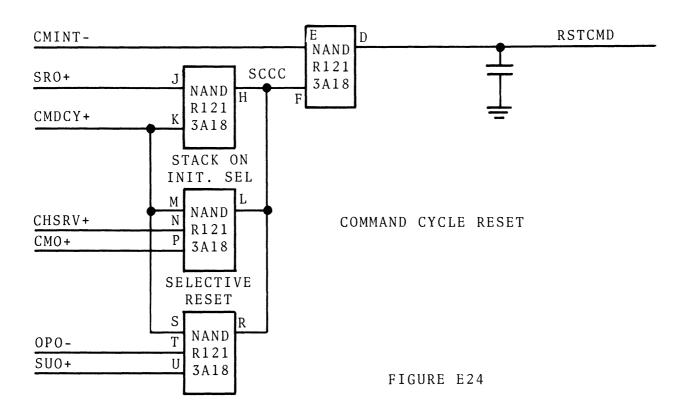

| 21            | Cycle Reset                                             | 59   |

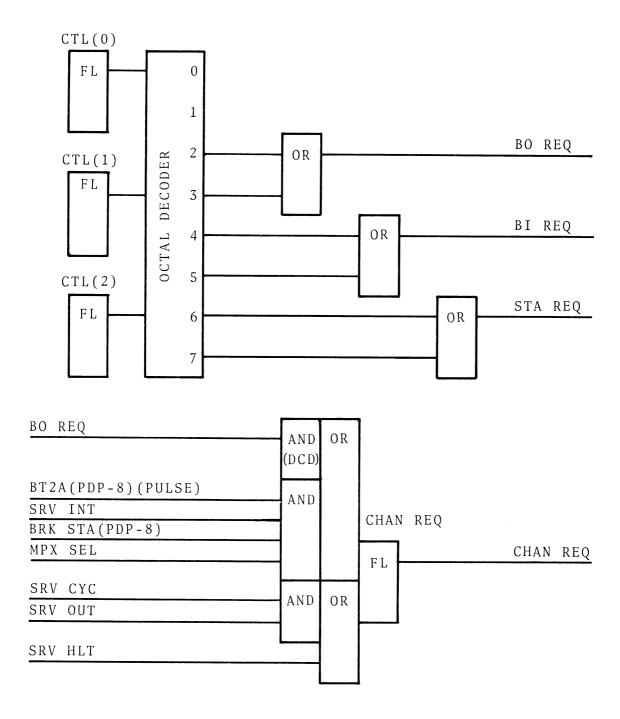

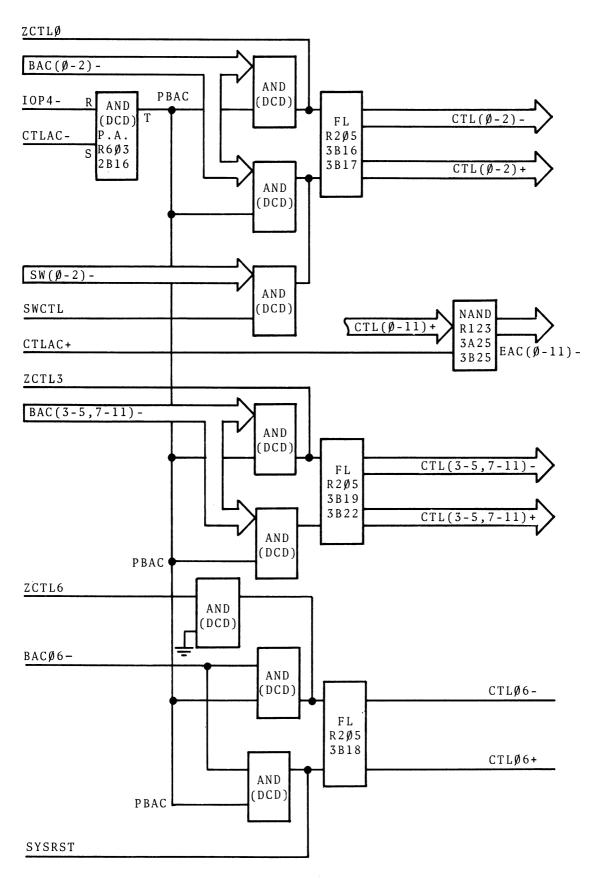

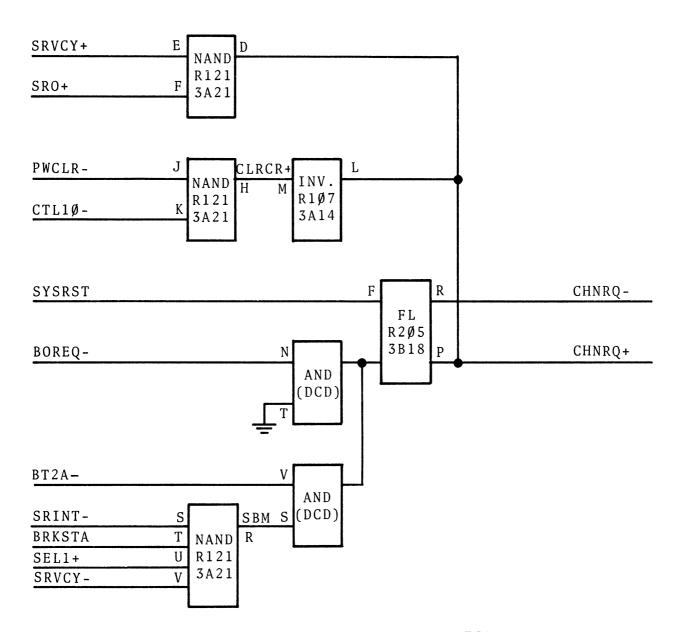

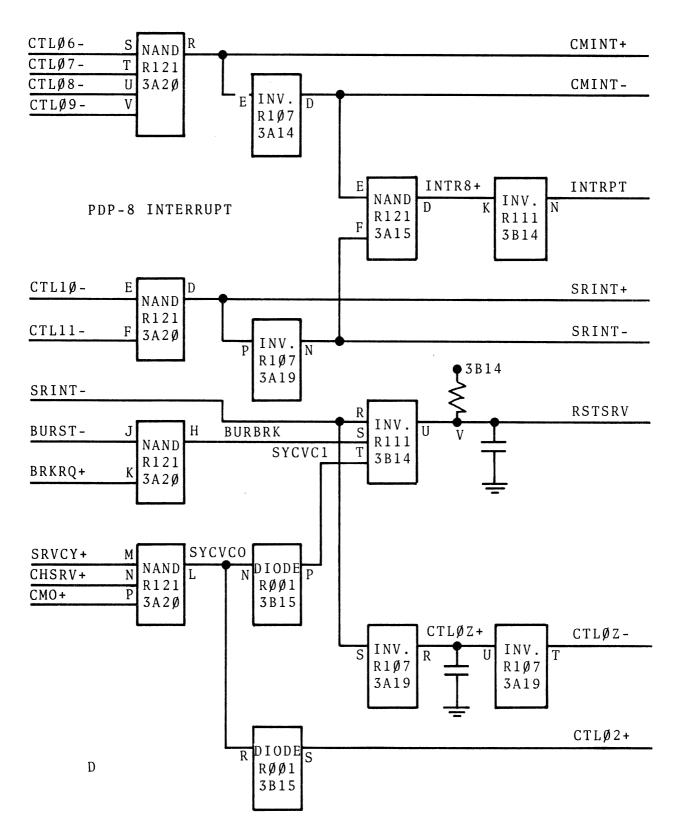

| 22            | Control Operation Decoder and Channel Request Flip-Flop | 60   |

| A 1           | Channel Seizure                                         | 64   |

| A 2           | Command Byte Storage                                    | 65   |

| A 3           | Command Status Presentation                             | 66   |

| A 4           | Special Status Presentationxiii                         | 67   |

# LIST OF FIGURES (cont'd)

| Figure |                                | Page |

|--------|--------------------------------|------|

| A 5    | Service Cycle                  | 68   |

| A 6    | Service Cycle End              | 69   |

| A 7    | PDP-8 Data Break Cycle         | 70   |

| B 1    | Initial Selection              | 73   |

| B 2    | Service Cycle                  | 73   |

| В3     | Control Unit Busy              | 75   |

| B 4    | Interface Disconnect           | 75   |

| B 5    | Channel Seizure                | 77   |

| В 6    | Gate Transfer                  | 77   |

| В7     | Major State-Service Cycle      | 79   |

| B 8    | Data-Break Service Cycle       | 79   |

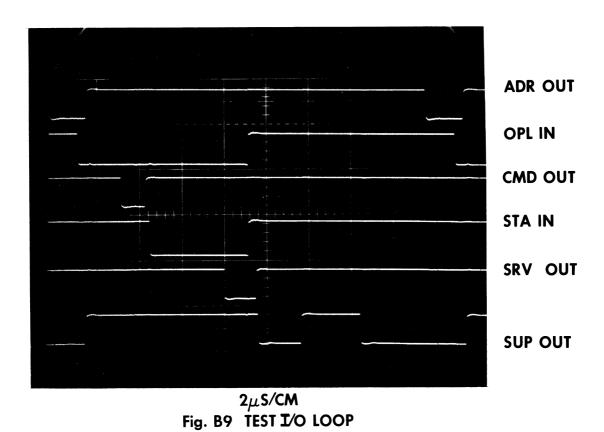

| B 9    | Test I/O Loop                  | 81   |

| B10    | SEL OUT/SEL IN Delays          | 81   |

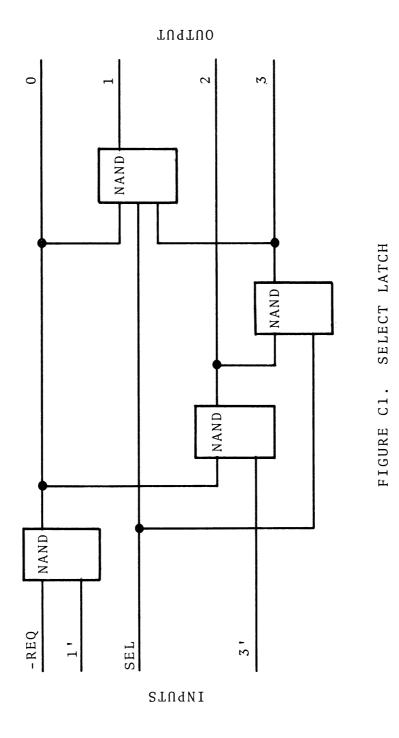

| C 1    | Select Latch                   | 86   |

| C 2    | Select Latch State Table       | 87   |

| D 1    | Physical Configuration         | 91   |

| D 2    | Power Control Unit             | 93   |

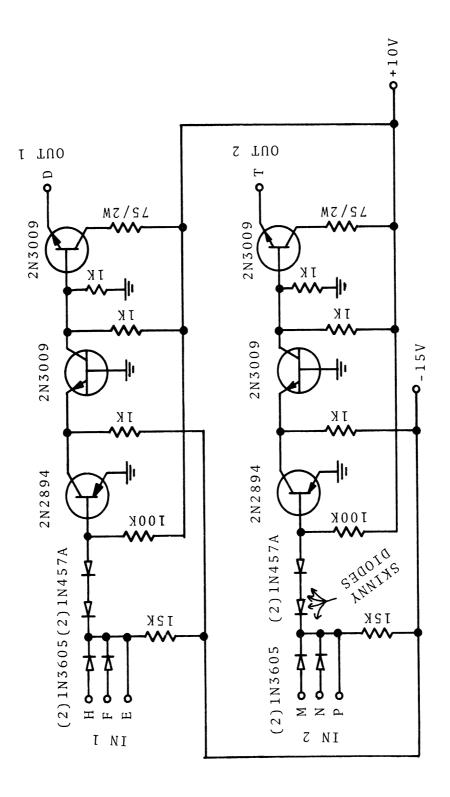

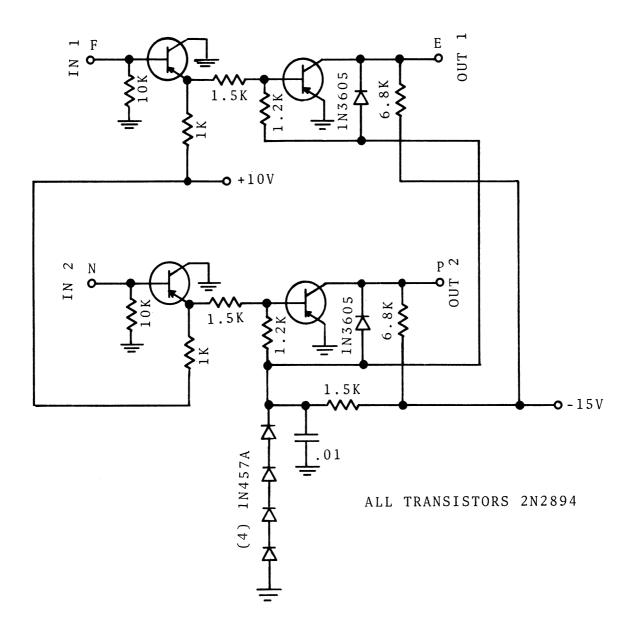

| D 3    | DEC to IBM Bus Driver Module   | 95   |

| D 4    | IBM to DEC Bus Receiver Module | 97   |

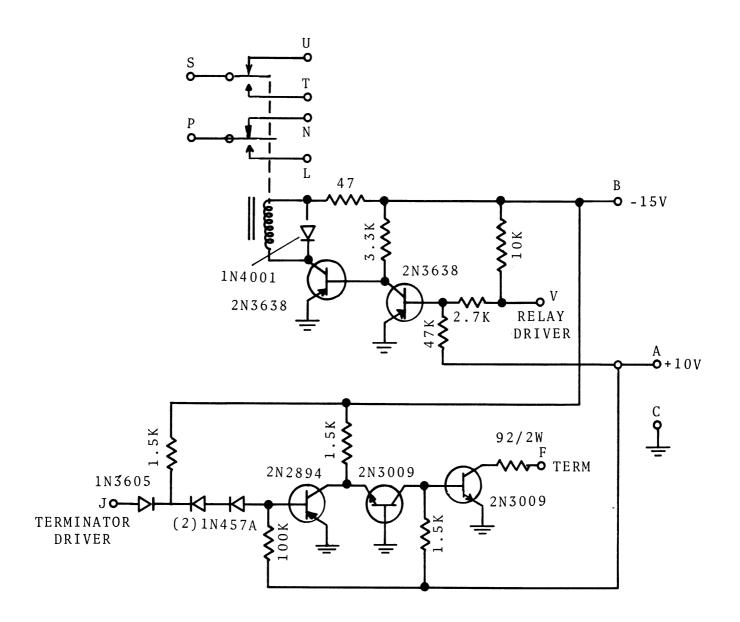

| D 5    | SEL OUT Bypass Module          | 98   |

| E 1    | AR1                            | 101  |

| E 2    | BR1                            | 102  |

| E 3    | AR1/BR1 Pulsing                | 103  |

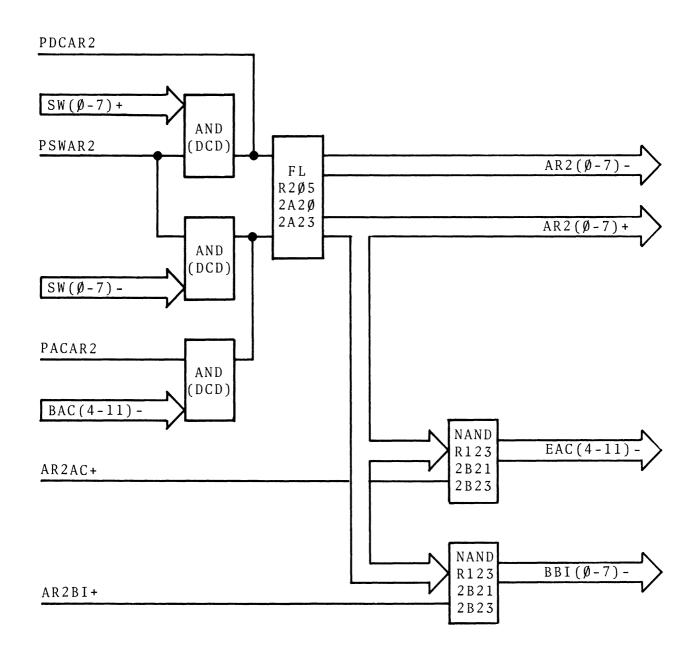

| E 4    | AR2                            | 104  |

| E 5    | BR2                            | 105  |

| E 6    | AR2/BR2 Pulsing                | 106  |

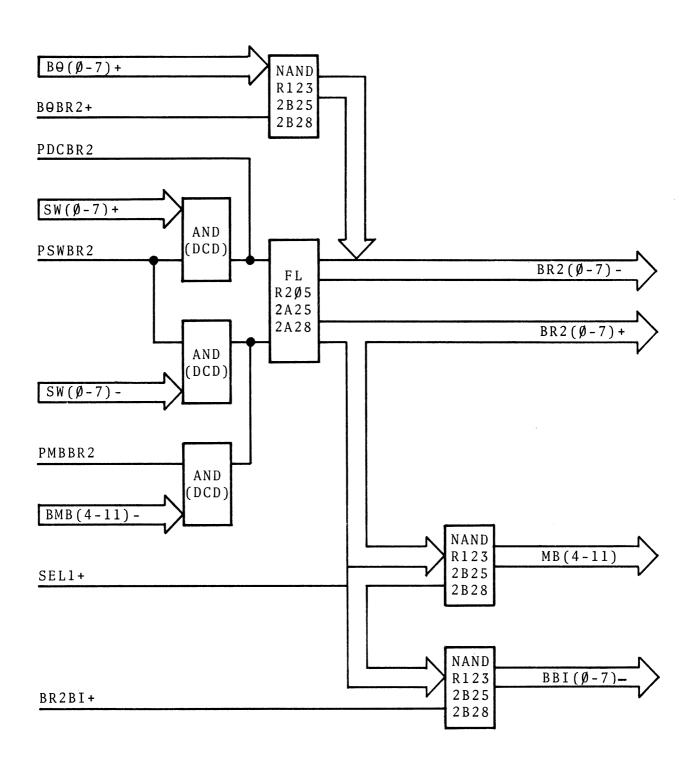

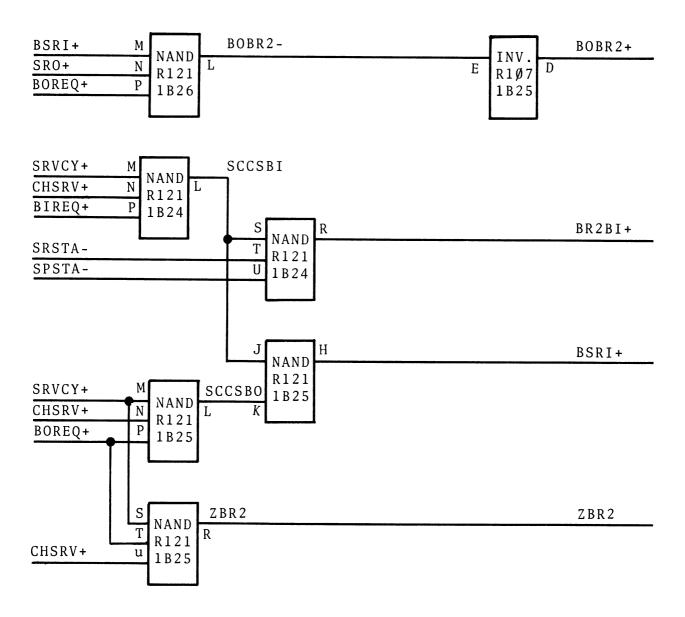

| E 7    | BR2 Gating                     | 107  |

| E 8    | Control Register               | 108  |

| E 9    | Clearing the Control Register  | 109  |

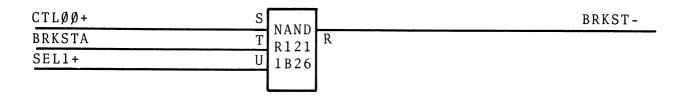

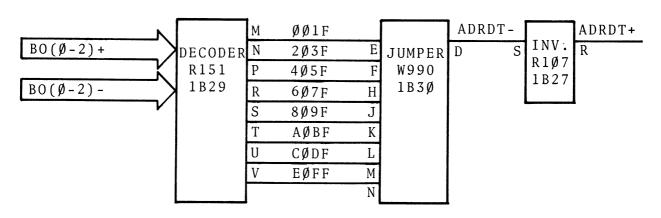

| E10    | Control Operation Decoder      | 110  |

| E11    | IOT Detection                  | 111  |

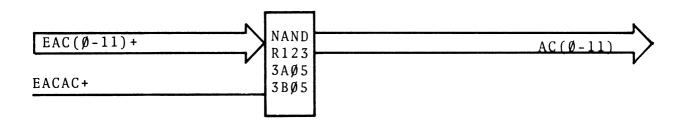

# LIST OF FIGURES (cont'd)

| Figure |                                           | Page |

|--------|-------------------------------------------|------|

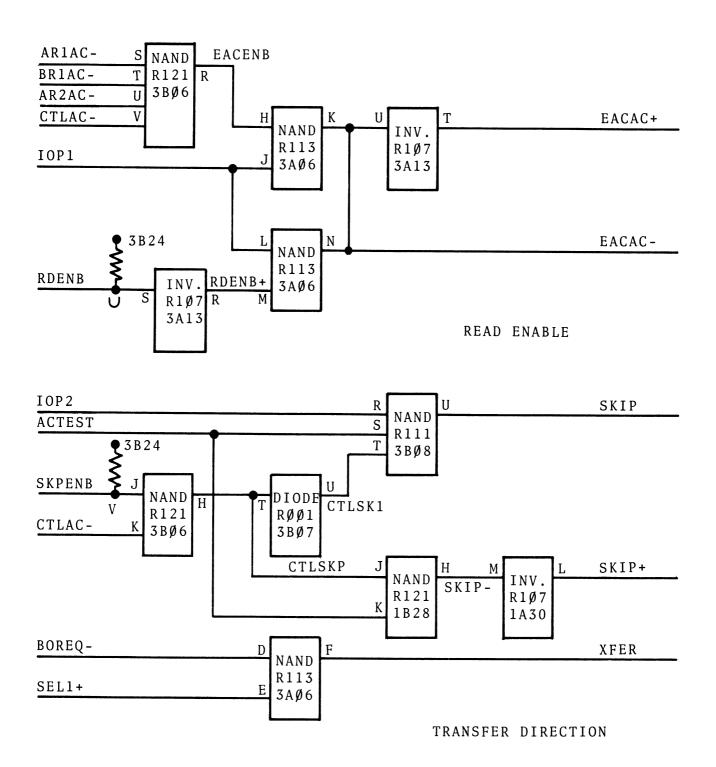

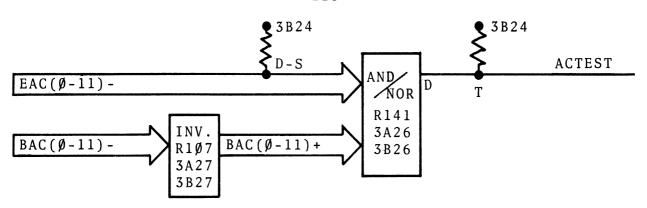

| E12    | Transfer Direction                        | 112  |

| E 1 3  | Address Register Compare                  | 113  |

| E14    | Address Detect                            | 114  |

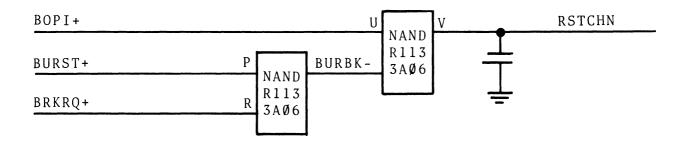

| E15    | Channel Request                           | 115  |

| E16    | Select Interception                       | 116  |

| E17    | Channel Seizure                           | 117  |

| E18    | Command Storage                           | 118  |

| E19    | Status                                    | 119  |

| E 2 0  | Command Cycle End                         | 120  |

| E 2 1  | Data Break                                | 121  |

| E 2 2  | Data Break                                | 122  |

| E 2 3  | Service Cycle Reset                       | 123  |

| E 2 4  | Command Cycle Reset. System Reset         | 124  |

| E 2 5  | BUS OUT Parity                            | 125  |

| E 2 6  | BUS IN Parity                             | 126  |

| E 2 7  | BUS OUT Parity Check. BUS IN Parity Check | 127  |

| E 28   | BUS-TAGS OUT Gating                       | 128  |

| E 2 9  | Select Out Gating                         | 129  |

| E 3 0  | BUS-TAGS in Gating                        | 130  |

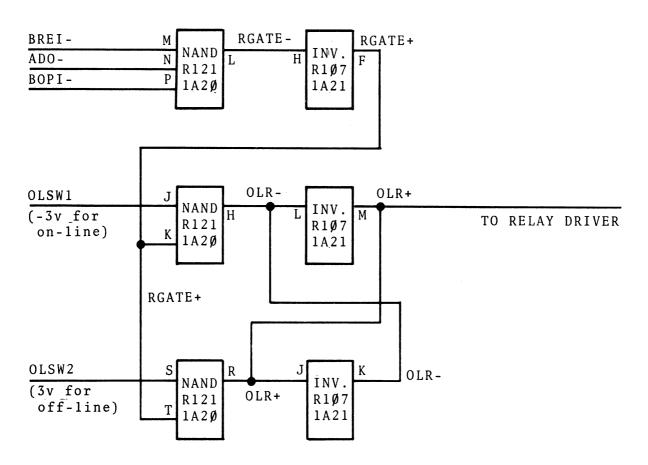

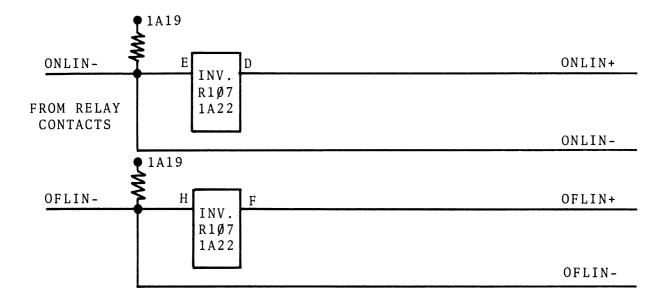

| E 3 1  | On-Line/Off-Line Circuitry                | 131  |

| E 3 2  | Test Panel Push Button Gating             | 132  |

| E 3 3  | Connectors Positions                      | 133  |

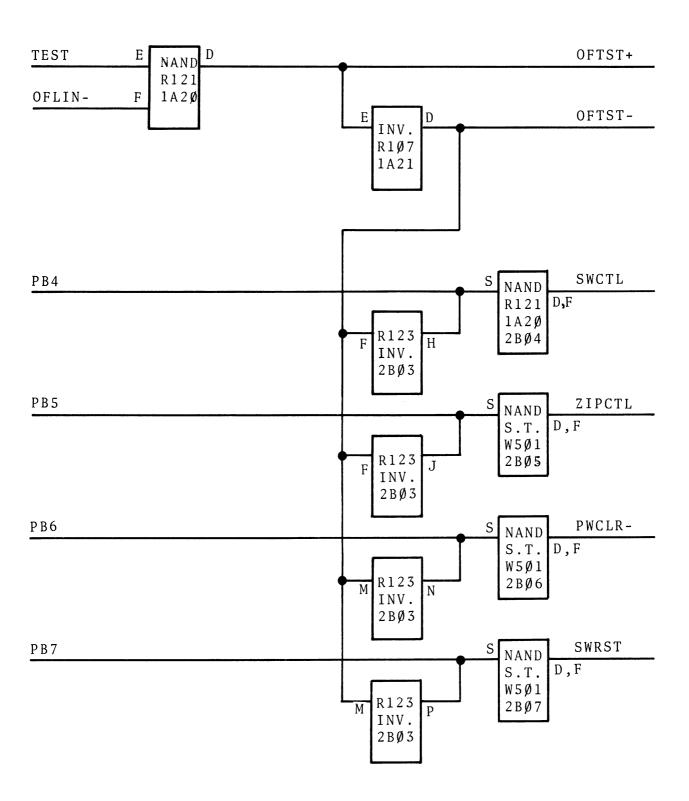

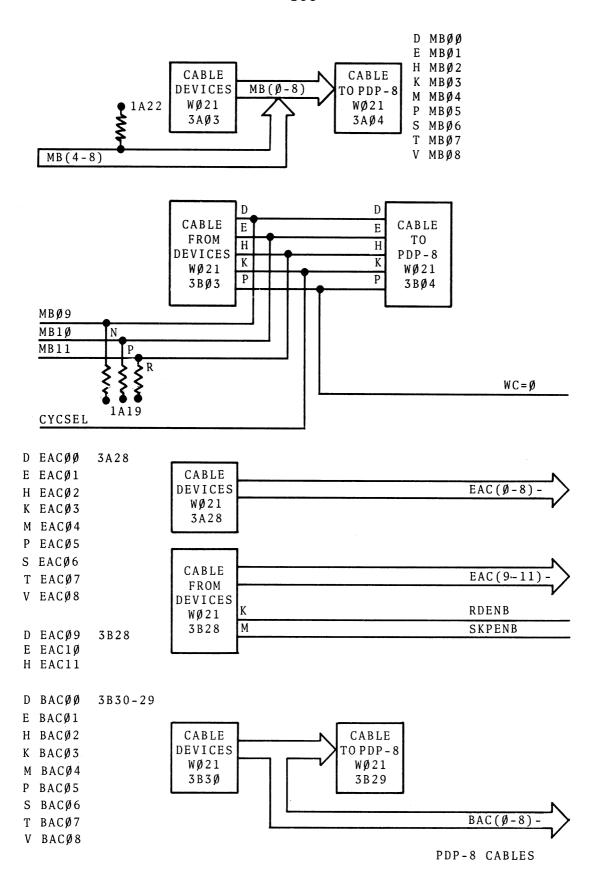

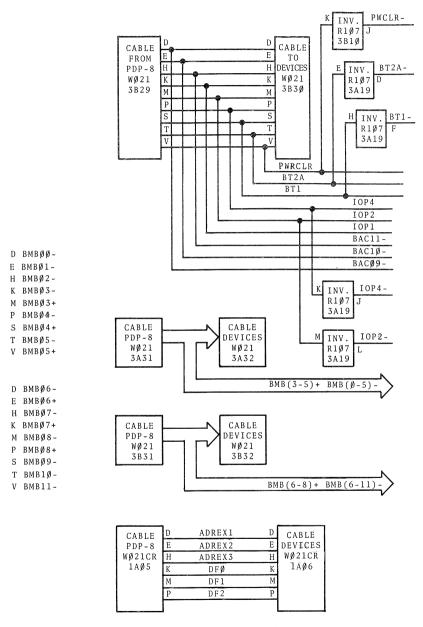

| E 3 4  | PDP-8 Cable Connectors (Page 1 of 3)      | 134  |

| E 3 4  | PDP-8 Cable Connectors (Page 2 of 3)      | 135  |

| E 3 4  | PDP-8 Cable Connectors (Page 3 of 3)      | 136  |

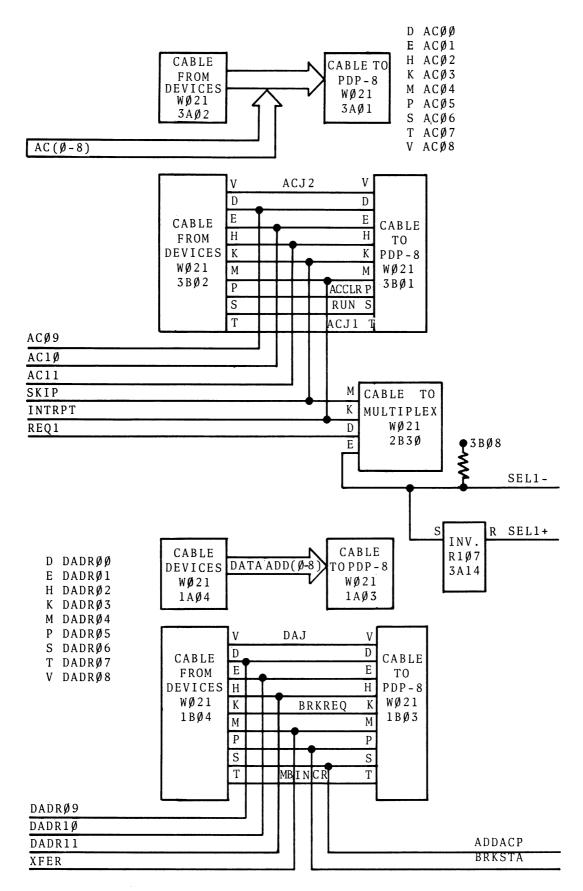

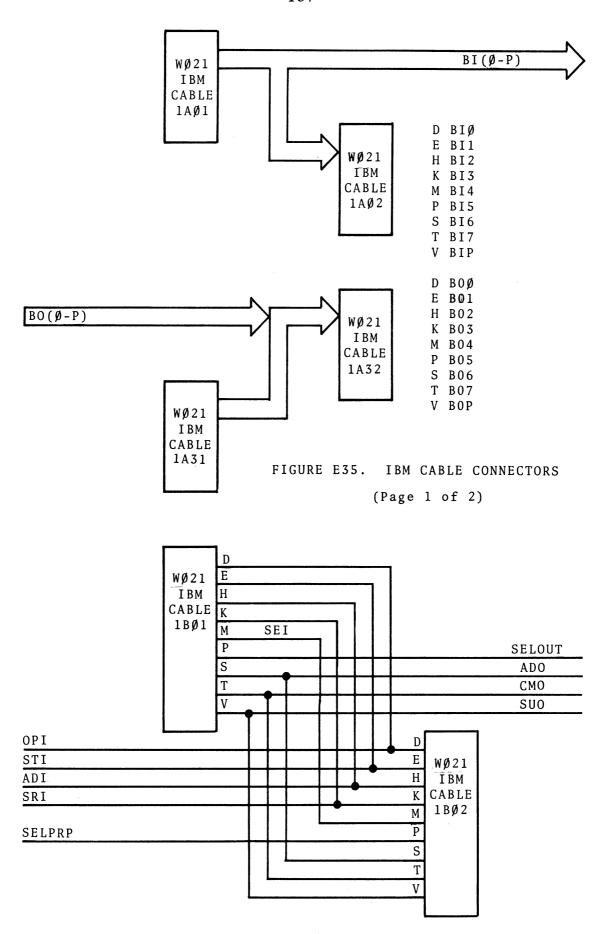

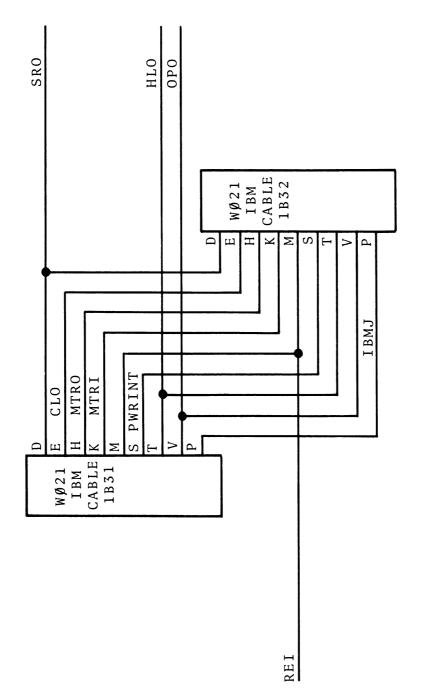

| E 3 5  | IBM Cable Connectors (Page 1 of 2)        | 137  |

| E 3 5  | IBM Cable Connectors (Page 2 of 2)        | 138  |

| E 3 6  | Test Panel Connectors (Page 1 of 3)       | 139  |

| E 3 6  | Test Panel Connectors (Page 2 of 3)       | 140  |

| E 3 6  | Test Panel Connectors (Page 3 of 3)xvii   | 141  |

# LIST OF FIGURES (cont'd)

| Figure |            |        | Page |

|--------|------------|--------|------|

| F 1    | Test Panel | Layout | 148  |

### SYSTEM/360 INTERFACE ENGINEERING REPORT

#### I. INTRODUCTION

The System/360 interface appears to the resident System/360 control program as similar to the 2702 Transmission Control. This approach is felt more fruitful in the face of heavy commitments to software support provided by the manufacturer. Its pertinent features are as follows:

- a. The interface recognizes a class of device addresses that are assigned according to the conventions established by IBM.

- b. Recognition of command codes and generation of status responses are in most cases under the control of the resident PDP-8 control program.

- c. Several buffer registers isolate the two machines so that the exchange of control and data information does not affect the timing of other control units that may be attached to the channel.

- d. Data transmission between the two machines proceeds in a byte-interleaved or burst-mode fashion at an aggregate data rate which may be programmed by the PDP-8 and indirectly by the System/360.

The System/360 interface consists of two principal components: the command interface, which services initial commands issued by the System/360 control program through the multiplexor channel, and the service interface, which transmits data and status information between the two machines. Both of these interfaces operate independently and in an overlapped fashion except at the channel interface circuitry itself, which is necessarily sequential in operation. At the channel interface the entire PDP-8 system appears to the System/360 as a control unit and accesses the interface transmission lines in the fashion prescribed for these devices.

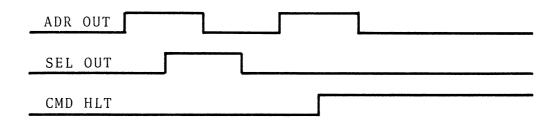

#### II. CHANNEL INTERFACE LINES

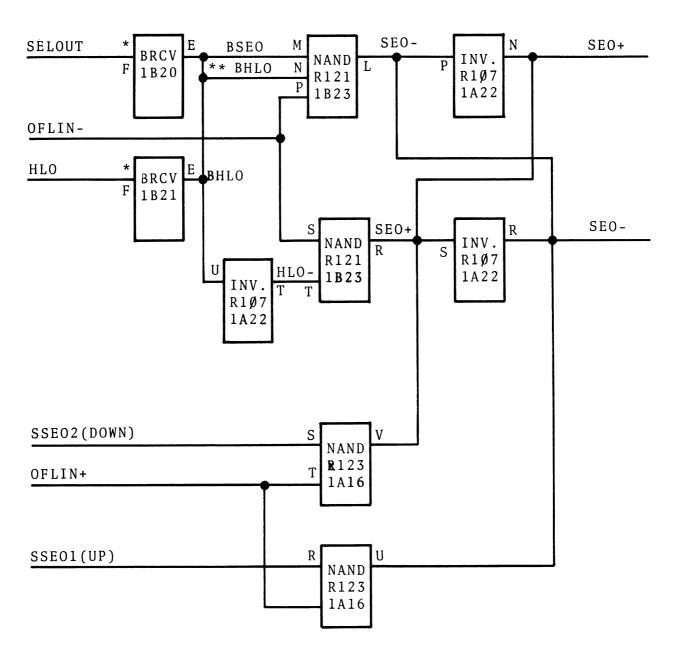

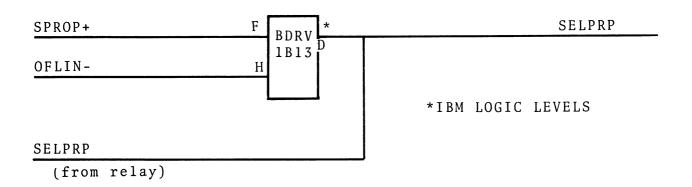

The System/360 interface is connected to the multiplexor channel via a set of 34 lines which are common to all other control units serviced by the channel. All of these lines except one are simply looped through the interface and attached to the various bus drivers or receivers as required. Thus in off-line or power-down situations it is not necessary to physically reroute or switch these lines, but merely to gate off the bus drivers and receivers. The one exception (the SEL OUT line) is physically broken at the interface. The interface-inbound SEL OUT line is routed to a terminator and bus receiver, while the interface-outbound SEL OUT line is routed from a bus driver. During normal equipment operation, signals received on the inbound SEL OUT line are processed internally and then propagated to the next control unit via the outbound SEL OUT line. During off-line or power-down conditions the terminator, bus receiver, and driver are bypassed with a relay.

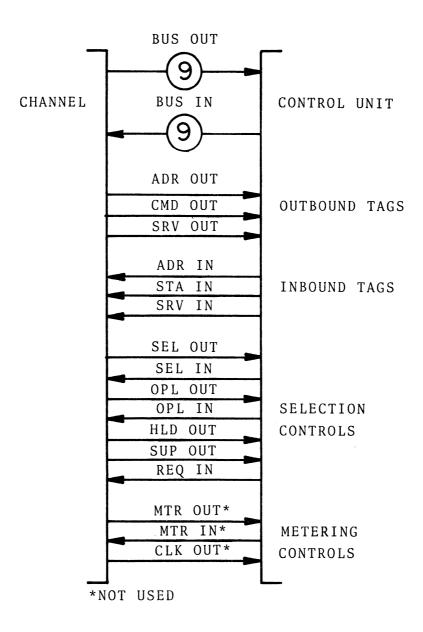

The interface lines and their nomenclature used throughout this document are summarized in Figure 1. Following is a brief description of the function of each of these lines. For greater detail, the reader is referred to the pertinent IBM publications.

BUS OUT. A set of nine lines, including a parity line, which propagates outbound information a byte at a time from the channel to all control units serviced by the channel. The information is conditioned by the outbound tag lines (ADR OUT, CMD OUT, SRV OUT) actuated by the channel and may represent a device address, a control unit command, or an outbound data byte.

<u>BUS IN</u>. A set of nine lines, including a parity line, which propagates inbound information a byte at a time from a selected control unit to the channel. The information

- 3 -

FIUGRE 1. CHANNEL-CONTROL UNIT INTERFACE LINES

is conditioned by the inbound tag lines (ADR IN, STA IN, SRV IN) actuated by the control unit and may represent a device address, a status byte, or an inbound data byte.

Outbound Tags. Three lines: ADR OUT, CMD OUT, and SRV OUT used to condition information on BUS OUT. If ADR OUT is up, the channel is attempting to gain initial selection of a control unit in order to transmit a command byte. When selection is achieved, CMD OUT indicates that a command byte is available on BUS OUT for interpretation by the control unit. SRV OUT is used as an interlock during data and status transmission cycles. These tags are also used in combination during certain control sequences not involving the use of BUS OUT.

Inbound Tags. Three lines: ADR IN, STA IN, and SRV IN used to condition information on BUS IN. If ADR IN is raised by the control unit, the information provided on BUS IN identifies the particular device requesting channel service. If STA IN is raised by the control unit, the information on BUS IN is the status byte pertaining to the device, and if SRV IN is raised, the control unit is requesting channel service for a data byte.

Selection Controls. Seven lines controlling the seizure and sequencing of transmission operations between the channel and the control unit. SEL OUT and SEL IN form a loop from the channel outbound through all control units in turn and finally inbound to the channel. A signal propagated on this line is intercepted by a control unit depending upon its position along this loop, which in effect establishes its priority for channel service. OPL OUT and OPL IN are conditioned by the channel and the control unit respectively and indicate the availability and connection

status of each of these devices. In particular, a control unit raises OPL IN when it has achieved selection on the interface, and is held up for the duration of the particular channel-control unit sequence involved. HLD OUT is used in conjunction with SEL OUT to minimize propagation delays through the select circuitry of the control units. SUP OUT is raised by the channel to inhibit control unit seizure of the interface under certain conditions. REQ IN is raised by each control unit requesting channel service and conditions the channel to poll the interface for seizure. Certain combinations of these selection control lines are used to indicate special conditions such as system and selective reset, and in conjunction with the outbound tag lines to indicate special conditions such as interface disconnect.

$\underline{\text{Metering Controls}}$ . Three lines used to condition usage meters on the various devices of a System/360 complex. The equipment described herein makes no use of these lines.

### III. CONTROL SEQUENCES

A number of control sequences are possible between the channel and the interface and, of these, most have several variations. All sequences can be grouped in one of three classes, however:

- 1. those involving initial-command selection,

- 2. those involving data transmission, and

- 3. those involving presentation of ending status.

For any one device, these sequences proceed in the order named; that is, the device is selected and logically connected to the channel, then transmits its data, and finally transmits status regarding the condition of the I/O device at the conclusion of

the operation. However, certain conditions can occur which are asynchronous to the progression of an operation through the states corresponding to the three principal sequences. Such conditions include those that halt data transmission and those that test device status during the course of an operation. Some of these can be produced by the channel without intervention by the program. The operation of the interface using typical sequences is summarized below. Additional details of operation in exceptional cases are discussed in the pertinent IBM publications.

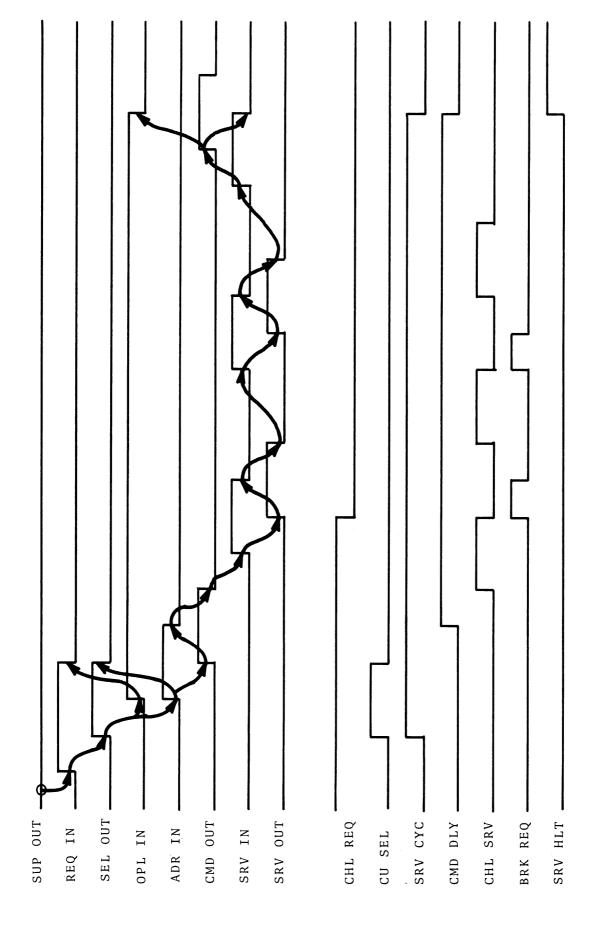

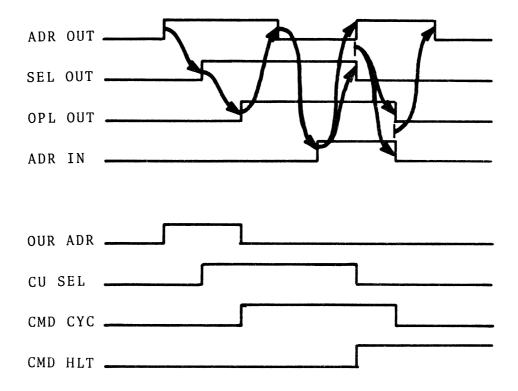

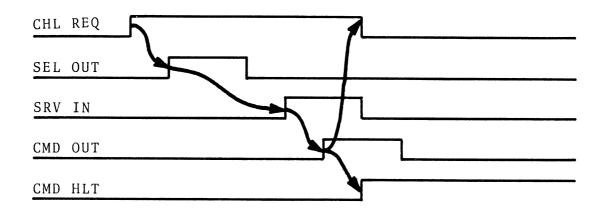

## 3.1 <u>Initial Selection Sequence</u>

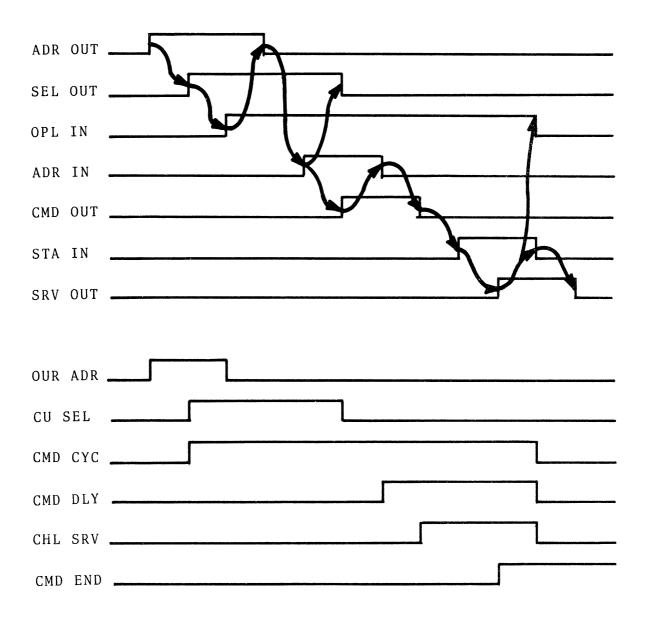

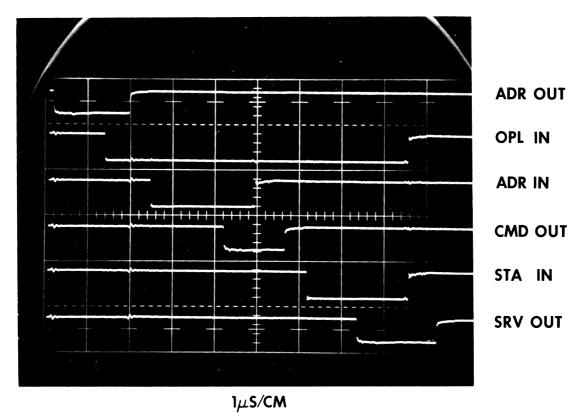

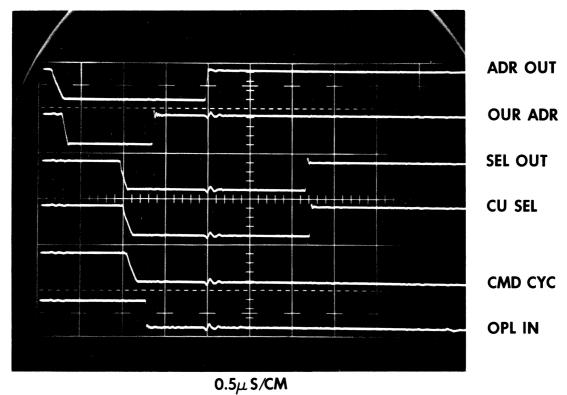

Figure 2\* shows the sequence of interface tag line signals during an initial selection procedure. This sequence is used for all channel commands and, in addition, for the Test I/O (TIO) sequence. The sequence begins when ADR OUT is raised by the channel while a device address is on BUS OUT. If the address has odd parity and lies within the block recognized by a control unit, that control unit prepares to seize the channel when SEL OUT rises on the interface. When this occurs, the control unit

- a. inhibits propagation of SEL OUT to the next lower-priority control unit on the interface,

- b. raises OPL IN to indicate to the channel that the control unit has in fact seized the interface, and

- $\ensuremath{\text{c.}}$  internally stores the device address presented on BUS OUT.

The channel then acknowledges OPL IN by dropping ADR OUT. The control unit then places the just-stored device address on BUS IN with odd parity and raises ADR IN. This returned address is checked by the channel for correct parity and for match

<sup>\*</sup> Wave forms shown in bottom of figures correspond to interface circuitry signals described in Section V. Timing information is given in the form of channel sequence photographs in Appendix B.

FIGURE 2. INITIAL SELECTION

against the address first transmitted on BUS OUT. If these tests fail, the channel performs a malfunction reset, which affects all I/O devices attached to the channel. Depending upon the particular machine model, this operation may result in a processor check or in a bit set in the Channel Status Word (CSW) stored as the result of the channel operation.

Following reception of a correct address on BUS IN, the channel next places the command byte (all zero bits for a TIO, nonzero for a valid channel command) on BUS OUT, and raises CMD OUT. The control unit stores the channel command internally and checks the byte for odd parity. Following this operation, the control unit drops ADR IN, which the channel acknowledges by dropping CMD OUT, an invitation for the control unit to present a status byte.

In most IBM control units, the allowable channel commands are well prescribed and represent only a few of the possible 255 codes. Accordingly, it is possible to detect immediately upon storage of the channel command byte whether the control unit can accept the particular command or not. Thus the control unit has the option of either accepting the command by presenting the channel with an all-zero status byte or rejecting the command with a status byte containing the unit check bit. In the equipment described here, the command may undergo analysis by the PDP-8 program, a process which may require a lengthy period compared to the channel selection sequence. Accordingly any channel command, other than TIO, is always accepted, even if it does not have odd parity. is up to the PDP-8 program to interpret the particular command code and to transmit possible rejection using an ending-status presentation containing the unit check bit.

Thus, following the acceptance of the channel command, the control unit places an all-zero status byte on BUS IN and raises STA IN, to which the channel responds with SRV OUT. The control unit now drops all inbound tag and bus lines and disconnects from the interface. If the channel forces burst mode at this time, SEL OUT will still be up at the control unit,

and a sequence of SRV IN-SRV OUT signals is expected by the channel to transmit the data associated with the operation. However, the multiplex channel will force burst mode only in connection with an Initial Program Load (IPL) operation. Therefore the equipment considered here is not normally expected to operate under channel-forced burst mode conditions.

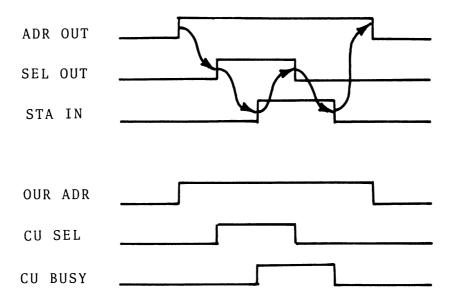

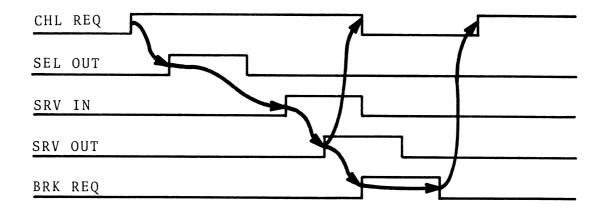

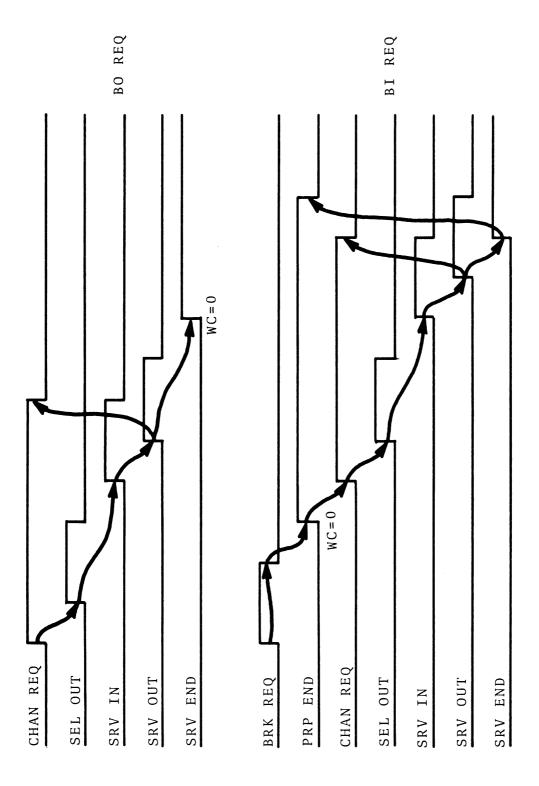

## 3.2 Service Cycle

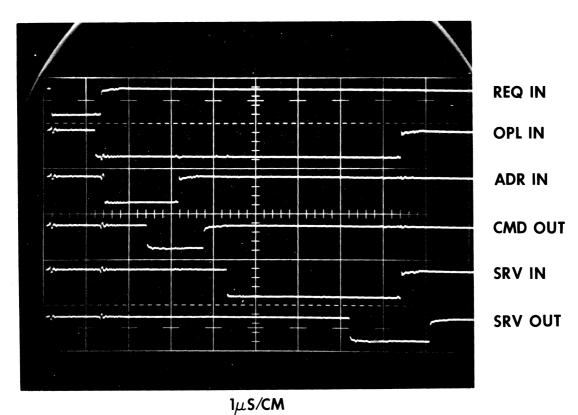

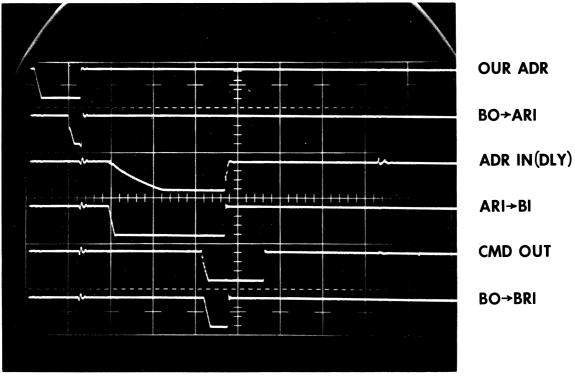

Figure 3 shows the sequence of interface tag line signals during a service cycle procedure. This sequence is used for all data and status byte transmission between the channel and the control unit. In the byte-interleaved mode, one such sequence is executed for each data byte separately. In the control-unit-forced burst mode, the initial part of the service cycle sequence is followed by alternate SRV IN-SRV OUT pairs.

The service cycle sequence differs from the initial selection sequence in that the transmission is initiated by the control unit rather than by the channel. A control unit requesting service raises the REQ IN tag line when the SUP OUT tag line is down at the control unit. (Certain sequences are expected to override the SUP OUT signal; see below.) When the channel next polls the control unit interface by raising SEL OUT, the highest priority control unit requesting service inhibits the propagation of SEL OUT, places its device address on BUS IN, and raises OPL IN and ADR IN. The channel checks the device address for odd parity, retrieves the addressed subchannel status in its active registers, and issues CMD OUT.

The control unit recognizes CMD OUT as permission to proceed with the operation, and it next drops ADR IN. When the channel drops CMD OUT the control unit raises either

a. STA IN and places a status byte on BUS IN,

FIGURE 3. SERVICE CYCLE (BURST MODE)

- b. SRV IN and places a data byte on BUS IN for transmission to the channel, or

- c. raises SRV IN and waits for a SRV OUT channel acknowledgment that a data byte has been placed on BUS OUT for transmission to the control unit.

If the device address does not have odd parity, the channel performs a malfunction reset. If a status byte does not have odd parity, an interface control check condition is generated. If, in the case of channel-inbound transmission, a data byte does not have odd parity, a channel data check condition is generated. Depending upon the particular machine model, these indications appear as a processor or memory check and as a bit set in the CSW stored as the result of the channel operation.

The channel acknowledges the receipt of a data or status byte, as appropriate, with SRV OUT. This response is also used by the control unit to verify the presence of a data byte on BUS OUT where appropriate. The channel may alternatively respond to SRV IN with CMD OUT, indicating that the data region in its main storage is exhausted, and may respond to STA IN with CMD OUT, indicating that the status byte is to be stacked in the control unit for later presentation to the channel.

In any case, the control unit responds to an outbound tag line at the end of the service cycle sequence by dropping all inbound tags and disconnecting from the interface. The channel is now free to continue polling for other control units on the interface or to issue new commands to the same or other control units. In particular, under some conditions, certain channel-generated commands may be directed to a busy control unit before device-end status has been serviced by the channel (see below).

### 3.3 Special Sequences

During the course of normal equipment operation and in certain abnormal situations, special control-unit interface sequences may be generated by the channel. These fall into two classes: those intended to stop device activity by request from the System/360 program, and those generated either by manual intervention or by the machine itself for the purpose of temporarily disconnecting the device from the system.

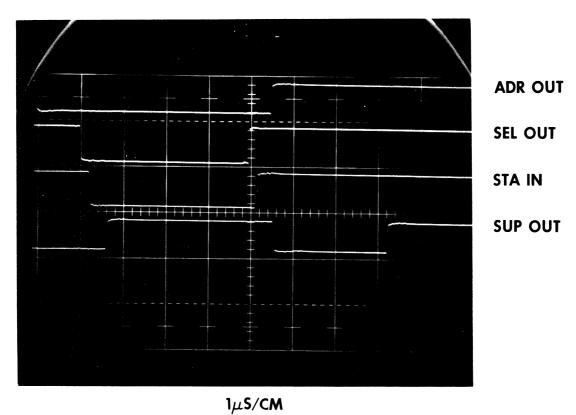

The first class of sequences includes the interface disconnect sequence generated by the channel in response to a Halt I/O (HIO) instruction executed by the System/360 program. Such a sequence can occur at any time, either within an initial selection or a service cycle sequence. The sequence is signaled after the device address has been checked by the channel and when ADR OUT is up at the control unit while SEL OUT is down. The sequence usually occurs before the command byte is stored on initial selection, but may occur after CMD OUT rises during a service cycle.

Figure 4 shows an interface disconnect sequence on initial selection. Following such a sequence, the control unit is expected to remove immediately all signals from the interface and to present ending status following its device operation. The ending status is to be transmitted only if the associated System/360 subchannel was working at the time of the sequence and may be cleared by a channel-generated TIO command prior to program intervention.

The second class of sequences includes the selective and system reset sequences generated by the channel in response either to manual intervention or equipment malfunction. The system reset sequence is indicated when both OPL OUT and SUP OUT are down at any control unit. This sequence occurs when power is first applied to the system, or when either the SYSTEM RESET, LOAD, or PSW RESTART pushbuttons are depressed on the System/360 operator's control panel. The selective

FIGURE 4. INTERFACE DISCONNECT

reset sequence is indicated when OPL OUT is down while SUP OUT is up at a control unit during an operation involving that control unit. This sequence occurs when the channel has detected a malfunction of the control unit or channel circuitry. Such a malfunction may involve invalid BUS IN parity, improper signal sequencing, or excessive sequence timings.

In the case of either the system or selective reset sequences, the control unit is expected to disconnect from the interface without presenting ending status for the operation. Since the control unit may be reselected immediately following a reset sequence, the control unit must appear busy to the channel while any internal time-dependent reset operations are completed.

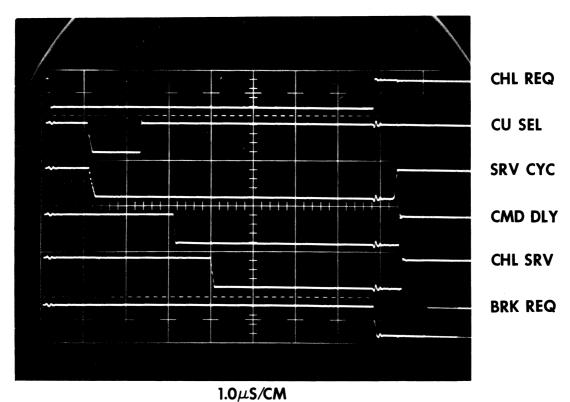

### 3.4 Polling Operations

Since both the channel, its attached control units, and their attached devices operate asynchronously with respect to each other, conventions for device polling and acknowledgment are required. The polling-acknowledgment conventions appear at three levels:

- a. during the initial selection of a control unit,

- b. during the channel seizure procedure by a control unit, and

- c. during the selection and deletion procedures of a device attached to a control unit.

Additional conflicts for both channel and subchannel access by the System/360 program are resolved by the channel and in some systems by the channel controller.

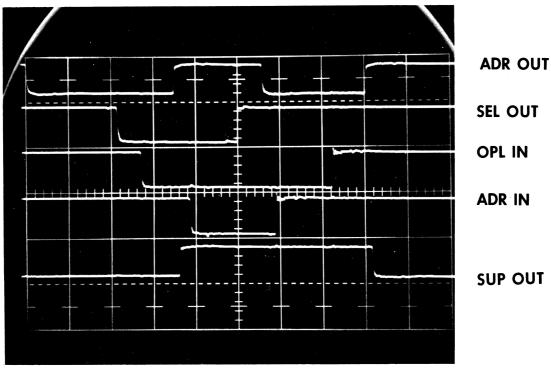

The channel selects an attached control unit with the initial selection sequence. If the control unit is free to accept a command (without respect to the status of its attached devices), it responds with the sequence shown in Figure 1. If not, then the control unit responds with the

control unit busy sequence shown in Figure 5. This sequence begins in the same fashion as the initial selection sequence; that is, the channel places a device address on BUS OUT and raises ADR OUT. When SEL OUT rises at the control unit servicing the device, and if the control unit is busy servicing some other device, the control unit responds by placing a status byte on BUS IN and raising STA IN. The channel responds with SRV OUT unconditionally, following which the control unit disconnects from the interface. Note that this sequence does not require the control unit to store the device address presented on BUS OUT or to present stored status for the device, even if it is available somewhere in the control unit.

The status byte presented to the channel during the control unit busy sequence may take two forms. One form includes both the status modifier and busy bits, which by convention inform the System/360 program that the control unit is busy and will present a status byte containing the control unit end bit at some future time. The other form includes all three of these bits, which by convention inform the System/360 program that the control unit is temporarily busy and that the operation which was rejected by the control unit should be immediately retried. The second form of status byte is used when the control unit busy condition is expected to last somewhat less than a millisecond, the interrupt processing time of typical System/360 programs, and the first form is used in all other cases.

When the channel is not busy with some internal operation and is not in the process of issuing an initial selection sequence directed to some attached control unit, the channel normally reverts to the polling mode. In this mode the channel interprets REQ IN as a request to poll the interface with SEL OUT, an operation that presumably will result in some control unit raising OPL IN. In some models of the System/360 product line, the polling mode may be entered at interesting times, for instance while the channel is retrieving the Channel

FIGURE 5. CONTROL UNIT BUSY

Address Word (CAW) or a channel command from main storage. Since the System/360 CPU is interlocked between the time that an I/O instruction is decoded and the time that the channel or the addressed device responds, it is important that the control unit sequence following REQ IN be as short as possible. In extreme cases of control unit delay during a Start I/O (SIO) operation (either addressed to the control unit or not), a processor check may occur when the System/360 CPU microprogram attempts to update its interval timer.

Data byte transmission operations for any particular device take precedence over all other channel operations, and are guaranteed to proceed without interference to the subchannels connected to other devices serviced by the channel. Status byte transmission operations, on the other hand, are considerably more involved and may take one of two alternate forms depending upon whether the subchannel in question is busy or not.

An ending status presentation to a busy subchannel must contain the channel end bit, but may contain others as well. Such a status presentation will always be accepted by the channel with a SRV OUT response to a STA IN during the service cycle. Once this status has been stored in local subchannel storage, the channel requests a System/360 CPU interrupt which causes a channel status word (CSW) containing the subchannel status to be stored in main storage. An ending status presentation to a subchannel not in the busy state will be automatically stacked in the control unit with a CMD OUT response to a STA IN tag during the service cycle. Before stacking the status at the control unit, however, the channel stores the device address of the requesting control unit in a special register called the Interrupt Buffer (IB) (or Interrupt Queue). At this time the channel requests a System/360 CPU interrupt, and, when granted, causes a channel-generated pseudo-Test I/O command to be issued to the device whose address is stored in the IB. The control unit in question now furnishes this status as the result of an initial selection sequence rather than the service

cycle sequence originally requested. Not all IBM control units can tolerate this interesting procedure; and, in fact, well-known machine hang-ups revealed in IBM documentation in connection with the 2702 Transmission Control are due to the failure of that device to process the pseudo-Test I/O.

#### 3.5 Equipment Failure Diagnostics

Most control unit component malfunctions can be diagnosed by the channel; and, in many cases, the System/360 control program can recover from the malfunction condition, record the failure, and continue system operation. In the case of the programmable control unit equipment considered here, certain invalid programming sequences can also produce such malfunction indications to the channel. Six malfunction conditions are recognized by channel circuitry as probably originating in an attached control unit. These may or may not be detected separately or as distinct from a processor check, depending upon the machine model:

- 1. Channel timeout. The System/360 CPU had not been released a pre-set interval (typically 150 microseconds) following issuance of an I/O instruction.

- 2. Address-in check. The channel detected a parity error on the address received from the control unit during a service cycle.

- 3. Status-in check. The channel detected a parity error on the status byte received from the control unit.

- 4. Incorrect selection. The address received from the control unit during an initial selection sequence does not match that transmitted by the channel.

- 5. No response. The control unit did not respond to re-selection on a chain-command operation.

- 6. Incorrect tag sequence. The control unit disconnected from the channel before the channel dropped the SEL OUT tag line.

Any of these malfunctions cause the channel to assume an interface control check condition, which may be indicated as a bit set in the CSW stored as the result of the operation and further detailed in the log-out area peculiar to the model. Condition 6 can occur on the multiplex channel only as the result of an Initial Program Load (IPL) operation and will always be produced when such an operation is directed to a control unit such as the 2702 Transmission Control or the interface equipment described herein.

# IV. PROGRAMMING CONSIDERATIONS FOR IBM SYSTEM/360 INTERFACE

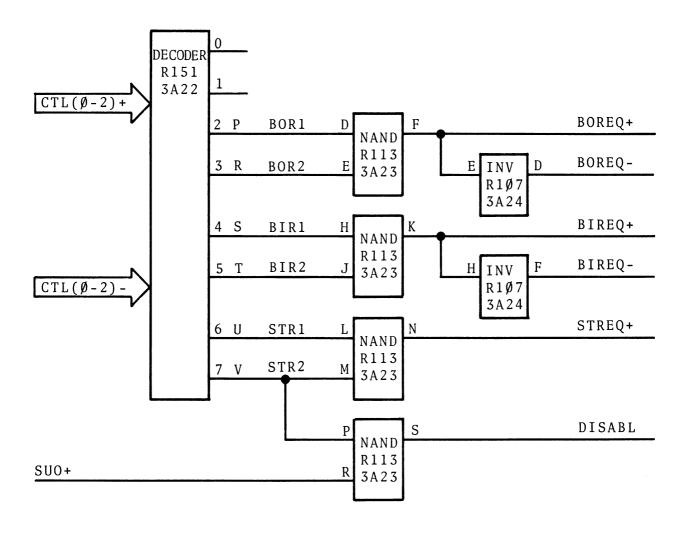

The System/360 interface is composed logically of two subinterfaces: the command interface and the service in-The command interface stores the channel command and device address developed during the multiplex channel initial selection sequence and presents the appropriate status byte to the channel to terminate the sequence. At the conclusion of the sequence, appropriate bits are set in a control register to indicate the particular type of sequence to the PDP-8 interrupt processor. The service interface supervises data break operations between the PDP-8 and the multiplexor channel. This interface is started by the PDP-8 program by loading a three-bit command code in the control register, following which three-cycle data break operations occur for data transmission between a block of PDP-8 memory and the channel. Both data and ending-status bytes are transmitted in this fashion. At the conclusion of the operation, either at channel-stop or word-count-equal-zero times, bits are set in the control register to indicate the termination condition to the PDP-8 interrupt processor.

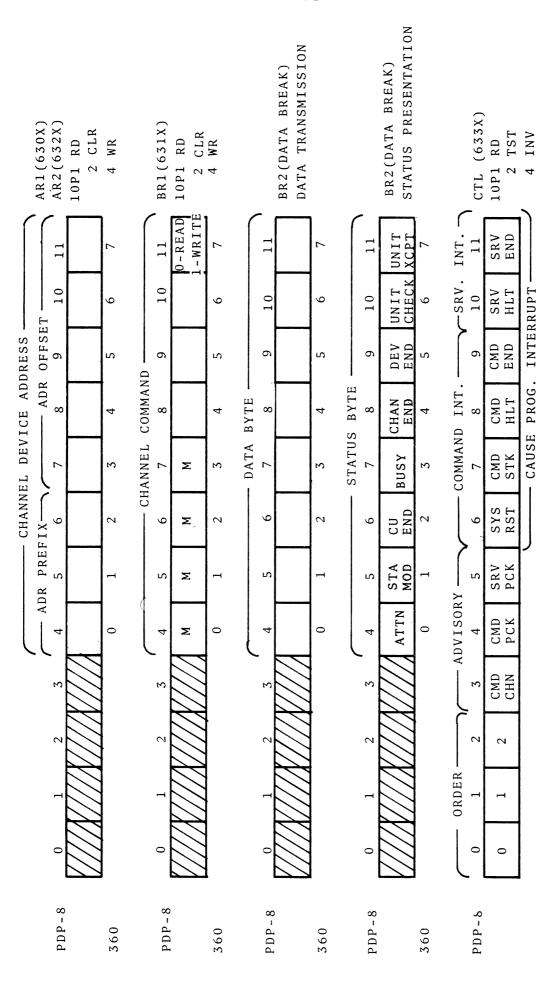

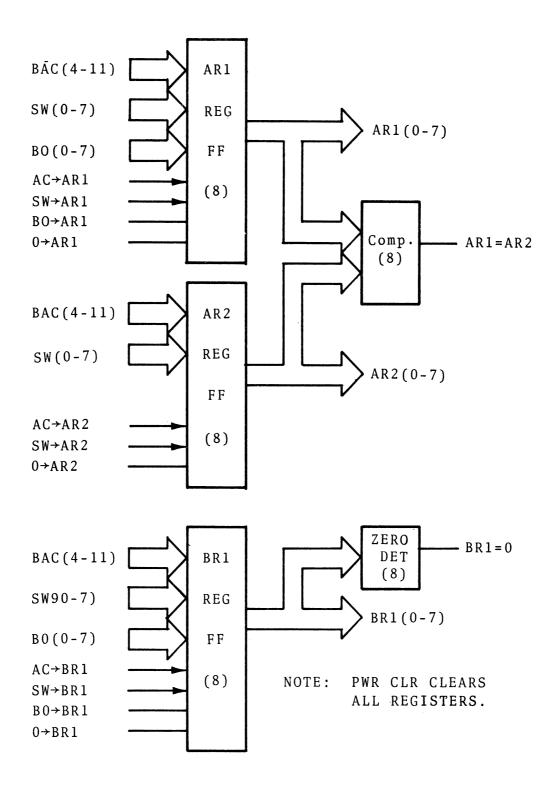

Five registers in the interface are available to the PDP-8 program. Two of these, AR1 and BR1, are used in connection with the command interface, while another two, AR2 and BR2, are used in connection with the service interface.

The fifth register, CTL, is common to both interfaces, and serves as the controlling element for the various operations. The AR1, BR1, and AR2 registers can be read, cleared, and loaded (one's-transfer) from the AC of the PDP-8. The BR2 register is connected only to the data break facility. The CTL register can be read, inverted, and tested bit-by-bit with appropriate microinstructions (see below). Some of these registers need not be read or loaded during the common interface operations; the general read/load facility is included primarily for diagnostic utilities. Figure 6 illustrates the coding of the various register bit assignments and establishes the IOT microinstruction codes for their access.

The operation of the control register invert-undermask (CTL INV) and test-under-mask (CTL TST) microinstruction is as follows: Both of these instructions address the twelve control register bits in one-to-one correspondence with the bits of the AC. The operation of the CTL INV microinstruction results in a bit-wise inversion of each bit in the control register for which the corresponding bit in the AC is a one. The operation of the CTL TST microinstruction results in a single-instruction program skip if each control register bit which is in correspondence with a one bit in the AC is a one. If any control register bit in correspondence with a one bit in the AC is a zero, no program skip is generated. An unconditional skip is generated if the AC contains all zeros.

The RD, CLR, and WR modifiers may be applied to the registers designated AR1, BR1, and AR2. The sequence of the IOP pulses is such that the micro-operations are performed in the order listed. The RD, TST, and INV modifiers may be applied to the register designated CTL. The micro-operations are performed in that order. Appendix F illustrates segments of code that are applicable in common programming situations.

FIGURE 6. REGISTER BIT ASSIGNMENTS

## 4.1 <u>Command Interface Operations</u> (Figure 7)

Three of the four System/360 I/O instructions will result in a channel sequence in the command interface, and two of these will normally end by interrupting the PDP-8 program. An SIO instruction executed by the System/360 will result in one or more channel commands being fetched from System/360 core storage and transmitted to a control unit. If the device address specified in the SIO instruction lies within the block recognized by the command interface and if the interface is not busy (i.e., holding a previously issued command), then the interface will seize the channel and store the device address in AR1 and the command byte in BR1. If the channel sequence is generated as a result of a valid channel command, the command byte stored in BR1 must be nonzero, and will be an odd number if channel-outbound service is indicated and an even number if channel-inbound service is indicated.

Note that in order for the selection sequence to be initiated, the parity of the device address must be odd. If this parity is odd and yet the parity of the command byte is not odd, then the CMD PCK bit of the control register is set. This situation, interpreted as a BUS OUT parity check, does not affect the progress of the selection sequence or the status byte subsequently transmitted to the channel.

At the conclusion of the initial selection operation, the CMD END bit of the control register is set if the channel accepted the interface-generated all-zero status byte and the CMD STK bit if the channel rejected the byte. If the channel sequence is generated as the result of a valid channel command, an occurrence of the later situation must be interpreted as a System/360 machine check.\* When either the CMD END or CMD STK bits are set, the PDP-8 is interrupted.

<sup>\*</sup> Note that in current System/360 channel equipment, stack on initial selection (CMD STK) never occurs on an all-zero status byte. In the case of a nonzero status byte, stack on initial selection will be generated only in certain cases

INITIAL SELECTION—STATUS ACCEPTED

INITIAL SELECTION—TIO STATUS STACKED

INITIAL SELECTION-HIO

FIGURE 7.

A Halt I/O (HIO) instruction executed by the System/360 causes a special channel sequence to be transmitted to a control unit. If the device address specified in the HIO instruction lies within the block recognized by the command interface and if the interface is not busy, then the interface will seize the channel and store the device address in AR1. BR1 will be forced to an all-zero byte. This sequence ends by setting the CMD HLT bit of the control register. A selective reset sequence generated by the channel during the progress of any command interface operation will also set this bit.\*\* When the CMD HLT bit is set, the PDP-8 is interrupted.

A Test I/O (TIO) instruction executed by the System/360 causes a special channel sequence which is identical to the SIO sequence except that the command byte contains only zero bits. If the device address specified in the TIO instruction lies within the block recognized by the interface and if the interface is not busy, then the sequence ends by the transmission to the channel of a status byte containing only the status-modifier bit. If the channel accepts this byte, the interface is released and the PDP-8 is not disturbed. If the channel rejects the status byte, then the CMD STK bit is set in the control register and the PDP-8 program is interrupted. It is the responsibility

involving command chaining. Since the command interface generates a nonzero status byte only in response to a Test I/O instruction, and since this "instruction" may not occur as an element of a channel-command sequence, it is not at all clear from extant documentation whether the CMD STK bit can ever be set in any likely programming situation.

<sup>\*\*</sup> A selective reset sequence is generated by channel equipment, at least in some models, in response to a status presentation of bad parity and possibly in response to an invalid tag-line sequence. A presentation of a device address of bad parity in conjunction with ADR IN will usually result in a channel-generated system reset sequence. A presentation of a data byte of bad parity is not always detected by the channel itself, but may be detected by the CPU or memory bus register circuitry and cannot be differentiated from parity errors due to other causes.

of the PDP-8 program to retransmit a status byte containing the status modifier bit via the service interface when allowed by the channel (however, see preceding footnote). Note that this behavior in connection with the TIO instruction is consistent with that of the IBM 2702 Transmission Control and implies, in particular, that the command interface cannot provide status in response to a program-generated TIO instruction. Note further that pseudo-TIO instructions can be generated by the channel without intervention by the program, and in these cases the command and service interfaces must cooperate in the successful transmission of a status byte to the channel. Such situations arise in connection with ending-status transmissions to subchannels not in the busy state (see below).

If a system reset sequence is generated by the channel, either as the result of power-up, initial program load, or manual operator intervention, the CMD RST bit of the control register is turned on. This operation clears all other bits of the control register and results in a PDP-8 program interrupt. All System/360 registers and subchannels are reset and placed in the available state. Pending data and status transmissions on the part of the PDP-8 should be suspended.

If any System/360 channel operation is directed to the command interface when either the CMD STK,CMD RST,CMD HLT, or CMD END control register bits are set, the command interface will immediately reject the operation with the control unit busy sequence, which involves the transmission to the channel of a status byte containing the status modifier, busy, and control unit end bits. This sequence is by convention interpreted by both the channel and the System/360 program as an indication to immediately retry the operation. For this reason, the resident PDP-8 program should give high priority to command interface interrupts, since the System/360 program may be hung up during the response interval. The PDP-8 interrupt processor clears such interrupts by inverting the

appropriate bit of the control register to a zero. Previous to this operation, meaningful contents of both the AR1 and BR1 register must of course be preserved in core storage by the interrupt processor. It is possible in some System/360 programming systems that tight TIO or HIO loops may be executed under certain conditions. In the case of the HIO instruction, the resultant load on the command interface will most certainly lock up the PDP-8 interrupt processor, which then must clear the System/360 condition, presumably by the transmission of ending status to the channel. In any case, the PDP-8 program must be aware of situations inherent in the particular parent System/360 supervisory programming system in which TIO or HIO loops are involved or in which the multiplex channel is masked against interrupts, and must give high priority to channel service under those conditions.\*

## 4.2 <u>Service Interface Operations</u> (Figure 8)

In all service-interface operations, a block of data is transferred either channel-inbound or channel-outbound. The three-cycle data break facility of the PDP-8 is used for this block transfer operation, which once initialized by the PDP-8 program, continues until the PDP-8 residual word count decrements to zero, until the channel detects that a System/360 core memory storage area is exhausted, or until the System/360 program issues an HIO instruction. All transmission operations make use of only the low-order eight

<sup>\*</sup> A typical instance of a tight TIO loop occurs after presentation of a unit check to certain present System/360 programming systems. Programming constraints imposed by other control units, in particular the 2841, require that a TIO be directed to the control unit immediately following a unit check. In such a case, the selector channel must be disabled before issuance of the TIO. In such cases, the same behavior may exist on the multiplexor channel, a behavior which is strongly disadvised, since not only the command interface but other IBM control units as well will hang up the system for some time.

SERVICE CYCLE (BYTE-INTERLEAVED MODE)

SERVICE CYCLE-STOP

Figure 8a.

SERVICE CYCLE-END

FIGURE 8b.

bits of a PDP-8 core memory location. The four high-order bits are ignored in channel-inbound operations, and are replaced by zeros in channel-outbound operations. Either data bytes or status bytes may be transferred using the appropriate interface order codes (see below). In the case of status byte transmission, the service interface will automatically represent status to the channel following a stack-status channel sequence.

All data and most status operations involving the service interface take place only when the associated System/360 subchannel is busy, that is when a valid channel command has been stored by the command interface. If the low-order bit of the channel command is a zero, then channel-inbound service is requested and the PDP-8 program must select the interface-outbound data operation. If the low-order bit of the channel command is a one, then channel-outbound service is requested and the PDP-8 program must select the interface-inbound data operation. Violation of these constraints will usually result in either a channel check, processor check, or storage check, depending upon the particular System/360 model.

Status presentation to the channel when the sub-channel is busy will not usually be stacked by the channel; and, if a status presentation happens to be stacked, it can eventually be cleared by re-presentation to the channel. If the subchannel is available to the System/360 program, then any status presentation will be automatically stacked and must be cleared by a channel-generated pseudo-TIO command. Such considerations dictate a careful organization of the PDP-8 program to avoid System/360 hangups due to conflicts at the command and service interfaces.

All service interface operations involve a programmed procedure which

- a. presets the word count and current address locations accessed by the three-cycle data break facility,

- $\ensuremath{\text{c.}}$  loads a three-bit order code into the control register.

The service interface then proceeds with alternate channel sequences and three-cycle data break operations until either the PDP-8 word count is decremented to zero, or until a stop sequence is generated by the channel. The appropriate bits are then set in the control register and the PDP-8 program is interrupted. The interrupt is cleared by inverting the appropriate control register bits to zeros.

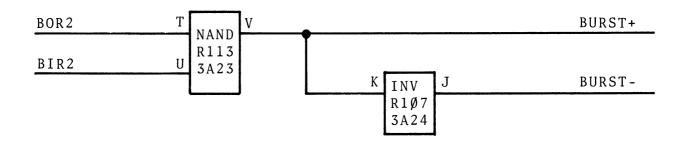

In the case of data operations, operation can be selected in either the byte-interleaved or burst mode. The byte-interleaved mode is appropriate for either low-speed operations with all models or both low- and high-speed operations with the higher-numbered models. Depending upon the width of the data paths to core memory and the degree of CPU involvement in the multiplexor channel operations, the burst mode may be appropriate for high-speed operations with the lower-numbered models.

A channel-outbound byte-interleaved data operation is started by loading an octal 2 into the high-order three bits of the control register. An octal 3 starts the same operation in burst mode. These orders initiate a data operation from the channel to the PDP-8 core memory. When the PDP-8 word count decrements to zero, the SRV END bit is set in the control register. When a stop sequence is transmitted by the channel in response to a service request by the interface, the SRV HLT bit is set in the control register. No data byte is transmitted to the PDP-8 core memory on a SRV HLT cycle.

This operation is suppressible. That is, if the channel is undergoing some critical sequence which should not be interrupted for lower priority operations, the service interface will suspend data transmission. Such is the case when another control unit on the channel is operating in burst mode or when certain status operations are pending at the channel. If an operation is not outstanding in the System/360 subchannel addressed by AR2, then, depending upon the model, the channel will either respond unconditionally with a stop sequence or an interface disconnect sequence, either of which sets the SRV HLT bit of the control register, or hang up the channel. If a data byte presented by the channel does not have odd parity, then the SRV PCK bit is set in the control register. This condition does not affect the further progress of the operation and in particular does not cause a PDP-8 program interrupt.

A channel-inbound byte-interleaved data operation is started by loading an octal 4 into the high-order three bits of the control register. An octal 5 starts the same operation in burst mode. This order initiates a data operation from the PDP-8 core memory to the channel. When the PDP-8 word count decrements to zero, the SRV END bit is set in the control register. The last byte fetched from PDP-8 memory on the SRV END cycle is transmitted to the channel. When a stop sequence is transmitted by the channel in response to a service request by the interface, the SRV HLT bit is set in the control register. The last byte obtained from PDP-8 memory on a SRV HLT cycle is then lost whether or not the SRV END bit is set during the same cycle.

The comments above under channel-outbound data transmission concerning data suppression and operation with an available subchannel apply also to channel-inbound data transmission. Odd parity is automatically generated on all channel-inbound operations whatever their nature, and the SRV PCK control-register bit is never affected by such operations.

When either the SRV END or the SRV HLT control register bits become set as a result of a service interface operation, the PDP-8 program is interrupted. The interrupt processor can determine how many data bytes have been successfully transmitted by inspecting the residual word count stored by the three-cycle data break facility and applying the modifying factors shown in Table 1. If the SRV HLT bit is not on at the conclusion of an operation, the opportunity exists to transmit additional data blocks. If both the SRV HLT and SRV END bits are set in the control register following a channel-outbound data operation, an interface failure is evident.

At the conclusion of the transmission of all data blocks, and in any case following any operation terminated by the SRV HLT bit, a status presentation is expected by the channel. Such a presentation must include the channel end bit and may include others as well. Following the presentation of channel end, the subchannel involved reverts to the interruption-pending state and may allow certain I/O instructions addressing the subchannel to proceed directly to the command interface. The subchannel reverts to the available state upon receipt of an interrupt response from the System/ 360 CPU, following which any I/O instruction may be directed to the command interface. The channel end and device end bits may be combined in a single status byte.

A standard status operation is one in which a status byte containing the channel-end bit is to be transmitted to a working subchannel. Such an operation is started by loading an octal 7 into the high-order three bits of the control register. This order initiates a status operation involving status byte transmission from the PDP-8 core memory to the channel. Usually only one byte will be transmitted to the channel on any one operation; but, regardless of the number of bytes actually transferred, the operation can legitimately terminate only when the PDP-8 word count decrements to zero,

TABLE I

| Order                    | SRV HLT   | SRV END | Sequence                                                         | *Bytes Transmitted                         |

|--------------------------|-----------|---------|------------------------------------------------------------------|--------------------------------------------|

| Data Outbound            |           |         |                                                                  |                                            |

| CTL 2 CTL 3              | 0 1 1     | 1001    | PDP-8 stop<br>channel stop<br>not possible (see text)            | M - N<br>N - N                             |

| Data Inbound             |           |         |                                                                  |                                            |

| CTL 4 CTL 5              | 0 1 1     | 1 0 1   | PDP-8 stop<br>channel stop<br>channel stop on last byte          | N - W $N - W$ $N - W - 1$ $N - W - 1$      |

| Status Inbound           |           |         |                                                                  |                                            |

| CTL 6<br>CTL 7           | 0 1 1     | 1 0 0   | PDP-8 stop<br>not possible (see text)<br>not possible (see text) | $N - W \\ N - W \\ N - W - 1 \\ N - W - 1$ |

| * N = initial word count | ord count |         |                                                                  |                                            |

N = initial word count

W = residual word count

a condition that sets the SRV END bit in the control register and interrupts the PDP-8 program. If an interface disconnect or selective reset sequence is transmitted by the channel in response to a status presentation, then the interface will immediately disconnect from the channel and cause the SRV HLT bit to be set in the control register.

The standard status operation is not suppressible by the channel. That is, status presentations cannot be locked out of the system if the channel is disabled but has an interrupt pending for another device. these conditions, a TIO instruction issued by the System/360 program can clear pending status at the service interface. Such a procedure is called for following presentation of unit check in a status byte to certain System/360 programming systems (see preceding footnote). Such systems regularly follow presentation of unit check by a Sense channel command while the channel is disabled, and rely on clearing device status using a TIO loop. Note that in such cases a busy indication is returned to the System/360 program as long as the subchannel is working; and, in particular, the TIO is not propagated to the device itself. Thus, if the subchannel is working, a standard status operation will always terminate with the channel accepting the presentation by the service interface, and in particular without the generation of pseudo-TIO commands on the part of the channel.

If a standard status presentation is once stacked by the channel for any purpose, then the interface itself automatically "demotes" the priority to that of a special status presentation. A special status operation is one in which a status byte is to be transmitted to a subchannel not in the working state. That is, a subchannel in either the available or interruption-pending states. Such an operation is started by loading an octal 6 into the high-order three bits of the control register. This order initiates a status byte transmission in the same manner as the standard operation, with

the exception that the presentation is suppressible by the channel. Such behavior is necessary to avoid the lockout of a channel-end status presentation of a lower-priority control unit on the channel interface cable by an unsolicited status presentation by the service interface. As in the standard operation, the special operation ends by setting the SRV END bit in the control register.

To summarize the application of the two kinds of status operations, the standard operation is used to transmit a status byte, which must contain the channel-end bit, to a working subchannel; and the special operation is used to transmit a status byte to a non-working subchannel. A failure to make this distinction will result in a machine hangup in the lower-numbered models of the System/360 product line and in an interface control check (channel timeout) in the higher-numbered models. Such situations may result in a diagnostic Channel Status Word (CSW) to be stored by the System/360.

If SUP OUT is up when SRV OUT is raised by the channel in response to an ending status presentation, the CMD CHN bit of the control register is set. Such an action is interpreted as an indication that the channel is command-chaining the previous operation and is about to reselect the interface for issuance of a new channel command. The indication of the CMD CHN bit is only advisory to the PDP-8 program and does not affect the progress of any channel or interface sequence. Depending upon the circumstances involved, the PDP-8 program may process this indication as a request to save such status presentations as the attention bit until the end of the System/360 channel program, or to assign high priority to command interface operations so that the immediately following reselection procedure will not delay the channel.

### 4.3 System/360 Control Program Operations

Interface programming considerations for the System/ 360 resident control programs are similar to those for the 2702 Transmission Control. However, due to the somewhat richer architecture of the interface, the behavior of the two machines will be slightly different. The main differences are:

- 1. channel-end and device-end status presentation do not necessarily have to occur in the same byte,

- 2. burst-mode operation can be sustained,

- ${\tt 3.}$  no immediate channel command operations are possible,

- 4. unsolicited status presentations are possible.

Considerations 1 and 2 imply that it is possible to use the interface on a shared subchannel, effecting a cost reduction in channel equipment on some models. However, since it is not possible to determine at initial selection time whether a particular device attached to the PDP-8 and logically connected to a particular System/360 subchannel can or cannot accept a channel command (consideration 3), use of this capability would be rather awkward. Consideration 2 implies that system performance at moderate data rates can be materially improved in the lower-numbered models by programming the PDP-8 to operate in short multi-byte bursts. The System/360 programming problems in connection with burstmode operations are similar to those arising in connection with tape control unit operations on the multiplexor channel. Consideration 3 is another implication of the general interface characteristic that all commands are accepted if the interface is not busy. Consideration 4 is an implication of the capability of the interface to clear asynchronous unsolicited status presentations as the result of a pseudo-Test I/O instruction.

Following is a short summary of the operation of System/360 I/O instructions when directed to a device address recognized by the interface. Only those features of operation dependent upon the peculiar characteristics of the interface are emphasized.

#### Start I/0

Issued to a nonworking channel and subchannel, this instruction will always result in a command interface operation involving the transmission of a channel command to If both the command and service interface the interface. are idle before transmission of the channel command, then condition code 0 is set at the conclusion of the Start I/O operation. I/O activity is begun and the subchannel is placed in the working state. If the command interface is busy, then condition code 1 (CSW stored) is set at the conclusion of the operation. The device status field of the CSW contains the busy, control unit end, and status modifier bits. No I/O activity is started and the command interface is undisturbed following this operation. Normally the indicated busy condition may be expected to last in the order of a few hundred microseconds, representing the interrupt processing time of typical PDP-8 programs. If the command interface is idle and the service interface is holding pending status for the device addressed by the Start I/O instruction, then condition code 1 is set at the conclusion of the operation. The device status field of the CSW contains the status presented by the service interface and in addition the busy bit. No I/O activity is started and both the command and service interfaces are idle following the operation.

#### Halt I/O.

Issued to a nonworking channel, this instruction will always result in a command interface operation without regard to the state of the subchannel. In addition, the

subchannel will be set up to signal the service interface to stop data transmission the next time a service cycle is requested. If the command interface is idle prior to the issuance of a Halt I/O instruction, then condition code 1 is set at the conclusion of the Halt I/O operation and the status field of the CSW is replaced with zeros. I/O activity is stopped by the addressed device, which will then provide ending status under control of the resident PDP-8 program. If the command interface is busy, then condition code 1 is also set following the operation, but the status field of the CSW contains the busy, control unit end, and status modifier bits. The Halt I/O indication has not been stored by the command interface, although the subchannel is set up to signal this condition when the service interface next requests a service cycle.

#### Test I/O

Issued to a nonworking channel and subchannel, this instruction will always result in a command interface operation but will not affect the PDP-8 program unless status presented is stacked by the channel. (And whether this can ever happen is highly dubious—see comments elsewhere in this document.) Condition Code 1 will always be stored at the conclusion of the Test I/O operation. If the command interface is busy prior to the issuance of this instruction, then the status field of the CSW will contain the busy, control unit end, and status modifier bits. If the command interface is idle and status for the addressed device is available at the service interface, then that status replaces the status field of the CSW. If neither of these conditions hold, then the single status modifier bit is placed in the status field of the CSW.

#### Programming Notes

Contrary to published doctrine, it is evidently possible to cause I/O interrupts from devices whose subchannels are working, but without including the channel end bit and without affecting the status of the subchannel. It is not at all clear whether this is possible on all models or whether unknown machine incompatibilities can occur. Use of this feature (for instance as an attention interrupt) in real-time control environments is obvious.

In some programming systems, an automatic Sense channel command is issued (with channels disabled) when a unit check bit is set in a status byte. These systems rely on a Test I/O loop to clear ending status from the Sense command. If the Test I/O loop is looking for device end, then the cooperating PDP-8 program must present channel end and device end together on the status byte which ends the Sense command. Alternatively, the PDP-8 program must arrange that a channel end status presentation for a particular device address be followed only by status pertaining to the same device. Otherwise conflicts between the channel and the interface can occur in which the channel is asking for status (via a programmed or pseudo-Test I/O) for a device that the service interface is just not prepared to surrender.

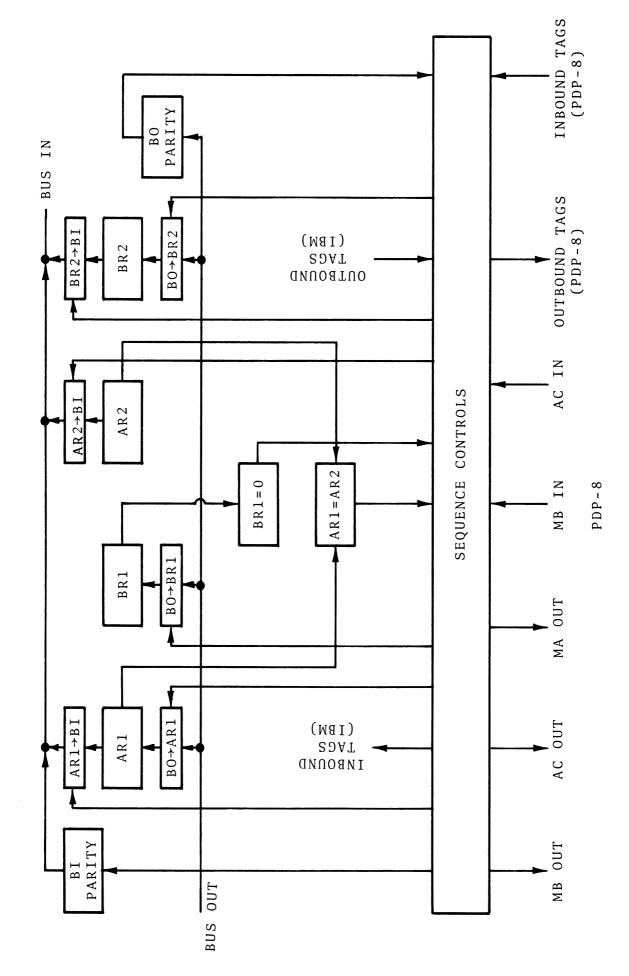

#### V. ARCHITECTURE OF SYSTEM/360 INTERFACE\*

The System/360 interface contains the registers and control circuitry to provide a bidirectional asynchronous transmission of both command, status, and data bytes between the System/360 multiplexor channel and the PDP-8. The interface consists of four data registers, their transfer gates, a control register, and various sequencing circuitry. The organization of these components is shown in Figure 9.

<sup>\*</sup> Logic symbology in this section corresponds to IBM standard usage. See Preface.

FIGURE 9. PRINCIPAL INTERFACE COMPONENTS

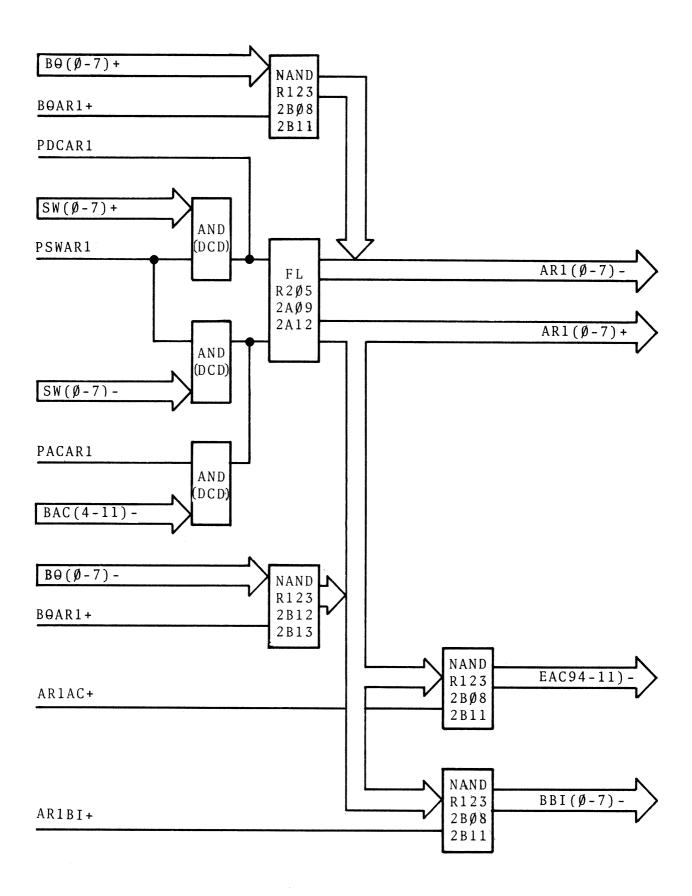

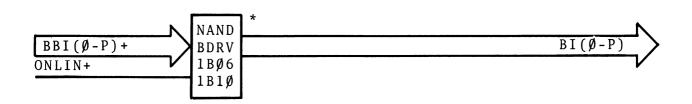

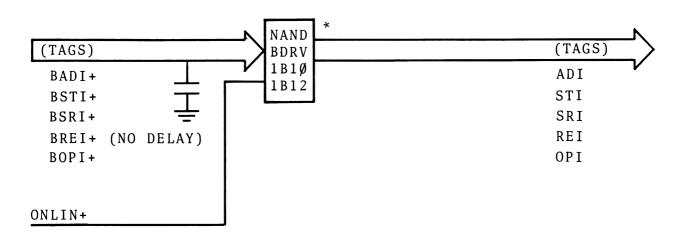

Referring to Figure 9, the four data registers are designated Address Register 1 (AR1), Buffer Register 1 (BR1), Address Register 2 (AR2), and Buffer Register 2 (BR2). four registers are provided with jam-transfer direct-coupled diode-capacitor-diode (DCD) gates from the test switches, and, in addition, all except BR2 are provided with onestransfer DCD gates from the PDP-8 AC. ARl is used to hold the device address presented by the channel during the initial selection sequence and is provided with jam-transfer directcoupled (DC) gates from BUS OUT. BR1 is used to hold the command byte presented by the channel during the initial selection sequence and is provided with ones-transfer DC gates from BUS OUT. AR2 is used to hold the device address presented to the channel during a service cycle. No inbound transfer gating is provided except for the DCD gates mentioned BR2 is used to hold a status or data byte during a service cycle and is provided with ones-transfer DCD gates from the PDP-8 MB and with ones-transfer DC gates from BUS OUT. BUS IN is provided with ones-transfer DC gates from AR1, AR2, and BR2 as well as constant generators 10, 40, and 70 (hex), which are used to synthesize certain status bytes. PDP-8 AC is provided with a special set of ones-transfer DC gates called the EAC bus, which is in turn provided with ones-transfer DC gates from AR1, BR1, and AR2. The EAC bus is used both to isolate the PDP-8 AC bus from the loading of the transfer gates and to provide a uniform interface for additional equipment, other than the interface, which may be connected to the PDP-8. The PDP-8 MB is provided with onestransfer gates from BR2. These gates are used in connection with a special data multiplexor described elsewhere.

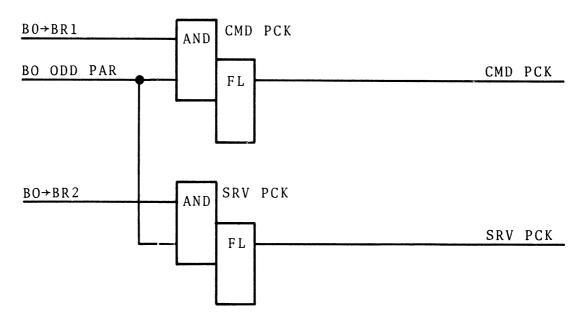

A nine-bit parity detector connected to BUS OUT indicates that odd parity is present on these lines and is used in conjunction with AR1, BR1, and BR2 when these registers are loaded from BUS OUT. A parity error during the

BR1 or BR2 loading operation will set the CMD PCK or SRV PCK bits of the control register respectively. An eight-bit parity generator connected to the BUS IN transfer gates provides odd parity for the BUS IN (P) line and is used in conjunction with all BUS IN operations.

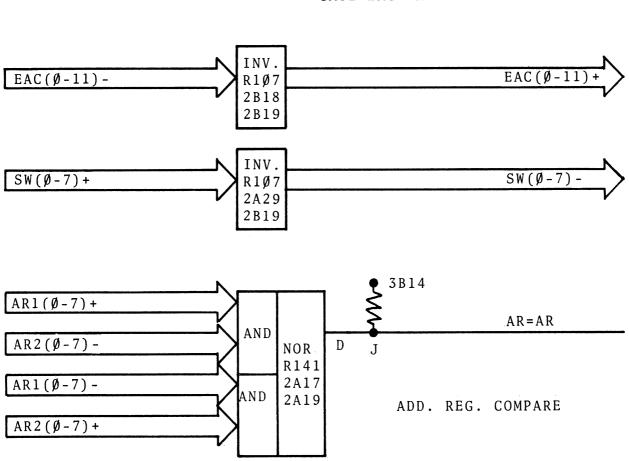

An eight-bit zero detector connected to BR1 is used during the initial selection sequence to detect the occurrence of a Test I/O channel command and to condition the following BUS IN status accordingly. An eight-bit compare circuit is connected to AR1 and AR2 to detect when these two registers contain identical bits and is used during the pseudo-TIO status sequence.

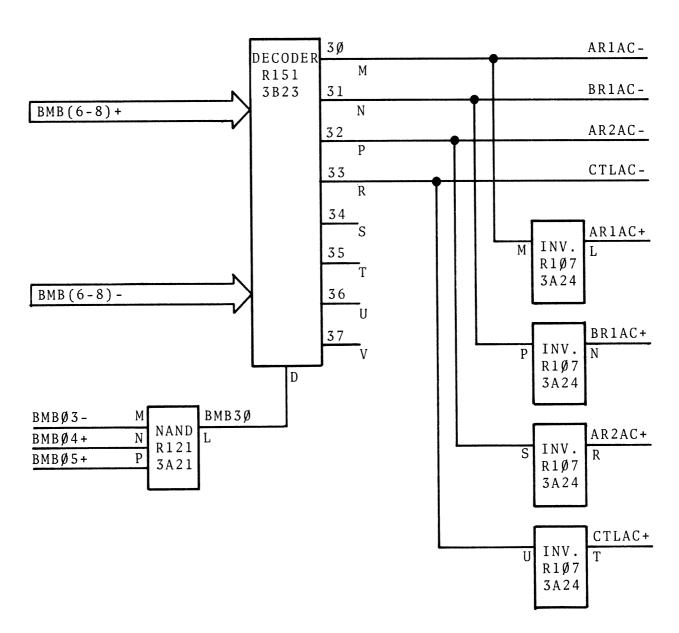

A three-bit decoder connected to BUS OUT is used during the initial selection sequence to determine whether the device address present on BUS OUT falls within the block serviced by the interface. Eight blocks of addresses, each consisting of a contiguous block of 32 addresses, may be selected by a jumper card.

The twelve-bit Control Register (CTL) is composed of a three-bit Order Register (OR) and a nine-bit Status Register (SR). The OR is used to hold the order code during a service cycle and is automatically reset following the conclusion of a block transfer operation. The SR is used to hold the various bits that indicate termination conditions of the interface sequences. However, the SR has no direct connection with any status byte that may be presented to the channel.

The logical details of these registers and their transfer gates are shown in Figure 10. Figure 11 shows the logical details of the PDP-8 data paths, and Figure 12 shows those of the BUS IN data paths. Circuit names, which appear only in this simplified description, are indicated on these diagrams. In some cases the actual circuit names and logical details differ from those recorded here. The logical details of the circuitry for all of these components are straightforward and are recorded in Appendix E. The logical organization of the control and sequencing circuitry, however, is

FIGURE 10a. AR1, BR1, AR2 REGISTERS.

FIGURE 10b. BR2 AND CTL REGISTERS

FIGURE 11. PDP-8 DATA PATHS

FIGURE 12. BUS GATING

central to the operation of the interface and is discussed below.

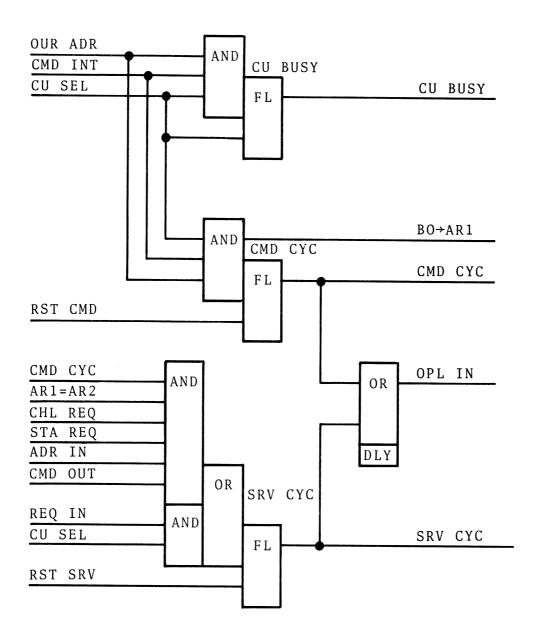

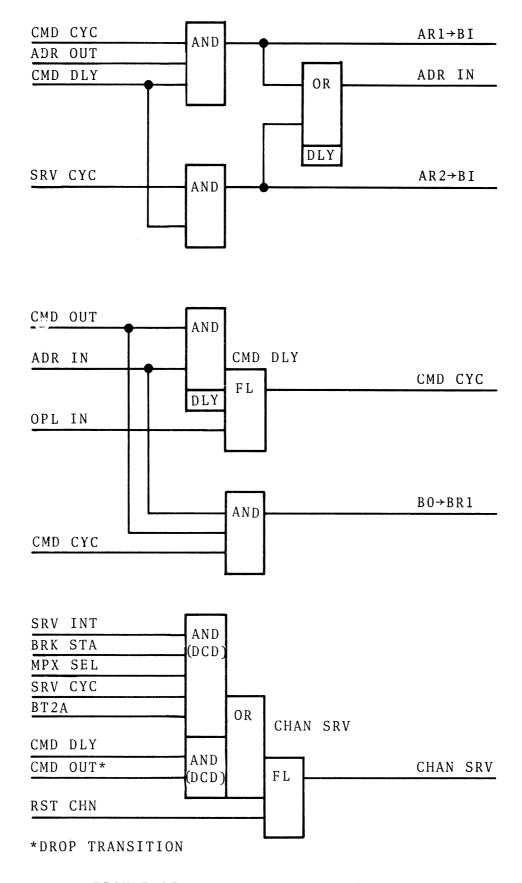

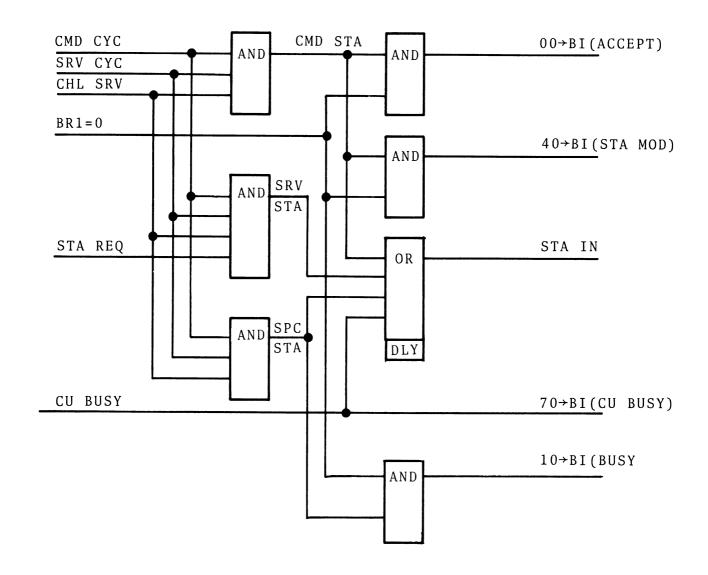

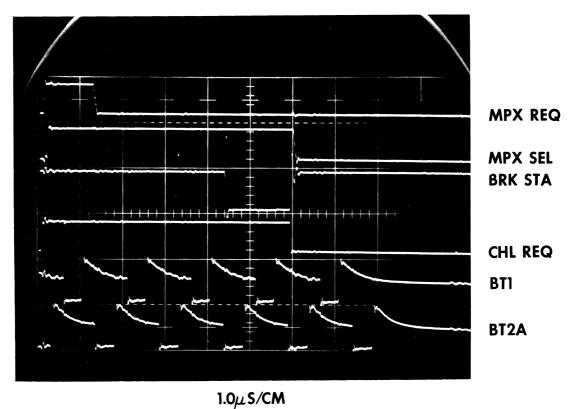

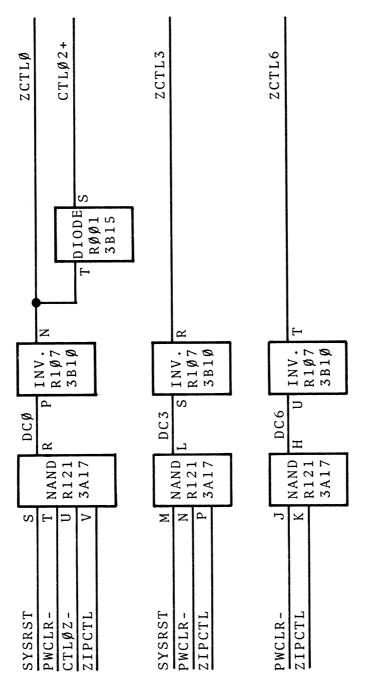

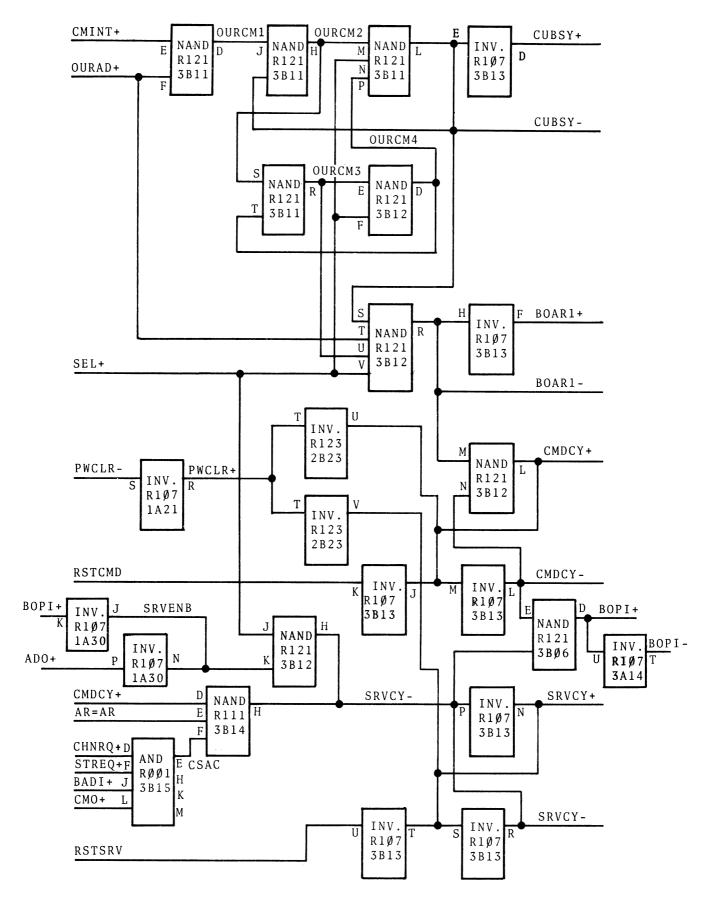

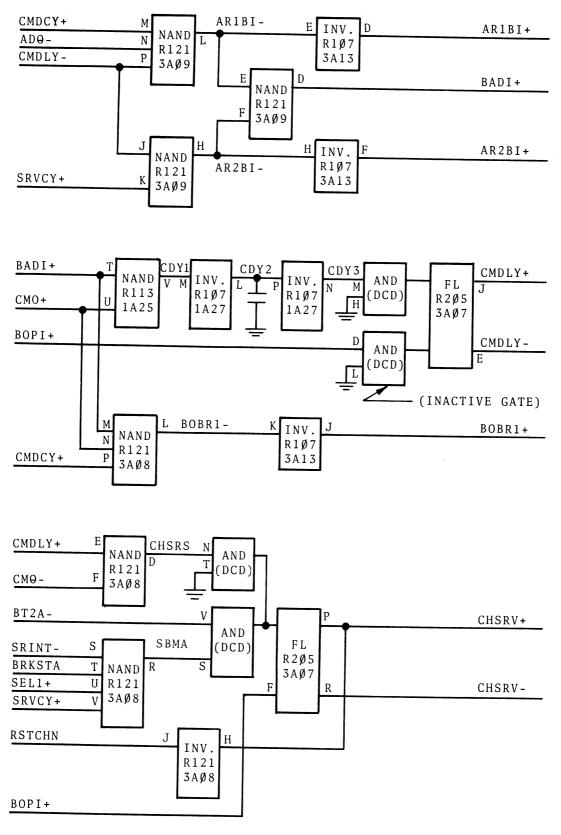

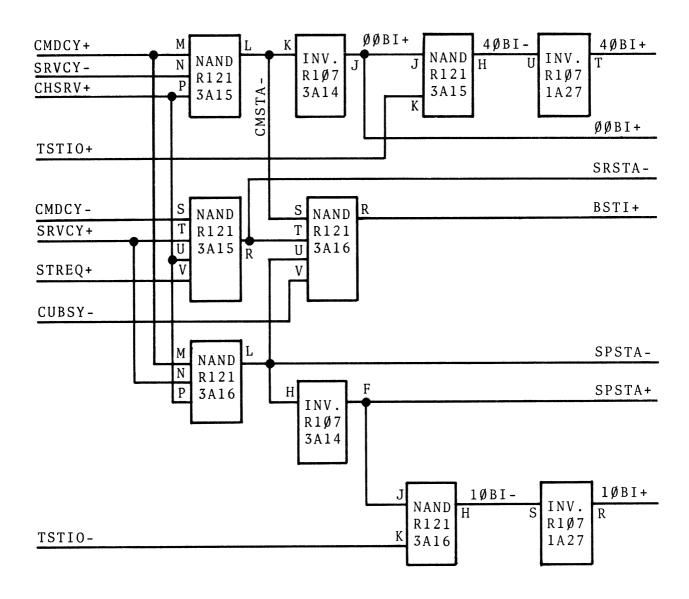

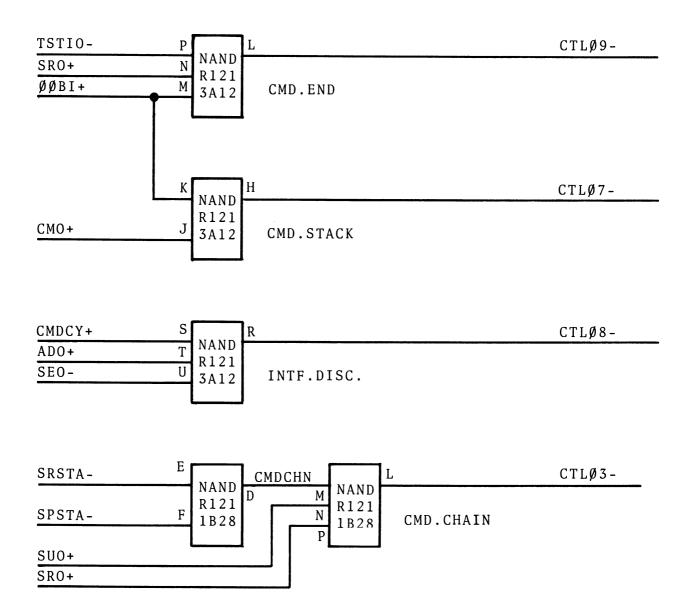

Figures 13 and 14 show respectively the logical organization of the circuitry used to intercept polling signals from the channel and that used to seize the control unit interface for the various kinds of sequences. During an initial selection sequence, the OUR ADR gate (Figure 13) detects the conditions for channel-requested service (initial selection) and the REQ IN gate detects the condition for control-unit requested service (service cycle). These gates may not respond simultaneously.

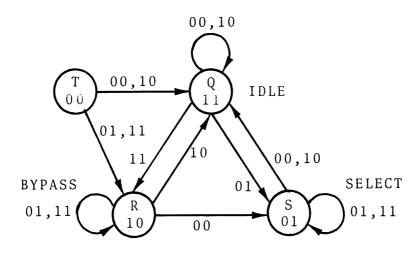

The remaining circuitry shown in Figure 13 is used in conjunction with the channel polling signal to detect the conditions under which the interface may seize the channel. The principal functional block in this circuitry is the select latch, shown in simplified form in Figure 13 but actually consisting of two interconnected flip-flops. This rather interesting circuit is a high-speed two-input switch with inputs derived from SEL OUT and from the two service-request gates OUR ADR and REQ IN. An analysis of this circuit is given in Appendix C.

When SEL OUT rises at the interface while either of the two service-request gates OUR ADR and REQ IN have true-valued outputs, the interface will fall into one of three states: CMD CYC, SRV CYC, or CU BUSY (see Figure 14). If OUR ADR is true and if the command interface is not busy (i.e., contains no previously stored command), then CMD INT is false and CMD CYC state is entered; if OUR ADR is true and if the interface is busy, then CMD INT is true and the CU BUSY state is entered. If OUR ADR is false and if REQ IN is true, then the SRV CYC state is entered. Entrance into either the CMD CYC or the SRV CYC state causes OPL IN to be raised after a short delay to allow the circuitry to stabilize, and entrance into the CMD CYC state causes the address presented by the channel on BUS OUT to be jam-transferred to

FIGURE 13. SELECT INTERCEPTION

FIGURE 14. CHANNEL SEIZURE.